# PARTICLE TRACKING AND IDENTIFICATION ON MULTI- AND MANY-CORE HARDWARE PLATFORMS

by

# PLÁCIDO FERNÁNDEZ DECLARA

A dissertation submitted by in partial fulfillment of the requirements for the degree of Doctor of Philosophy in

Computer Science and Technology

Universidad Carlos III de Madrid

Advisors:

José Daniel García Sánchez Niko Neufeld

September 2020

This thesis is distributed under license "Creative Commons Attribution – Non Commercial – Non Derivatives".

To my parents. *A mis padres.*

We have seen that computer programming is an art, because it applies accumulated knowledge to the world, because it requires skill and ingenuity, and especially because it produces objects of beauty.

— Donald E. Knuth [87]

### **ACKNOWLEDGMENTS**

Since I finished my master's degree and started working in the aerospace industry with GMV I have been interested in pursuing a PhD. But I did not find the right challenge or topic I was looking for. One day I received a call from my professor from Computer Science and Engineering degree and director of the master's degree I would later study in Leganés. He let me know about an opening position to do a PhD in High Performance Computing at CERN, in Switzerland. It was just what I was looking for; an incredible computing challenge working in the Large Hadron Collider. I applied for it and some interviews later I got the job.

I have to thank first and foremost my parents. It is thanks to them that I was able to purse any dream and challenge I ever imagined and I am ever thankful for their love and support. To my love and friend Afri, who helps me overcome any situation and makes any adventure an amazing journey to enjoy life.

I would like to thank my friends in Madrid for endless hours of explorations, discussions and joy in the good and bad times. To my childhood friends Javi and Josemari for every minute in the holm oak woods and the surrounding neighbourhoods. To Miguel, Guille, Centeno and all the group for adventure, climbing and nights in the mountains. To all the people that supported me in GMV... To Jordi, Albano, Patricio, Puma, Aven, Romo, Oso and Abel for many, many hours of rehearsal, all the concerts around Spain and experiences. To Cristian who took care of me in the river and plains. To Jorge for we supported each other to improve and finish our studies. To Auro and Álex who showed and accompany us on discovering the Alps, the lakes and the area. I am eternally grateful to my family who always have been supportive and encouraged me to achieve the career and life I wanted.

I am grateful to Niko and Omar for showing me the way in my doctoral studies. To Jose Daniel for the advice, guiding and conversations all along my career. To Daniel who made the experience at CERN so much more enjoyable. To Luismi for the discussions at CERN and exploring the mountains together. To Dorothea, Flavio, Rainer and Roel for all the help to make Allen an amazing thing. Thank you to all the people from the LHCb experiment and CERN that I worked with,

for showing me the way of physics, for the BBQs at Point 8, endless Factorio games and all the great discussions. Thanks to my colleagues at Universidad Carlos III de Madrid in the ARCOS research group. Firstly, I would like to thank to David del Río, Manuel Dolz and Javier Fernández for their help with the integration with GrPPI. Secondly, I would like to also thank Javier Garcia-Blas who helped me with the experiments in GPU architectures.

Thanks to the Spanish MINISTERIO DE ECONOMÍA Y COMPETITIVIDAD though project grant TIN2016-79637-P TOWARDS UNIFICATION OF HPC AND BIG DATA PARADIGMS, the EU Project ICT 644235 "REPHRASE: REfactoring Parallel Heterogeneous Resource-Aware Applications", Spanish "Ministerio de Economía y Competitividad" under the project grant TIN2016-79637-P "Towards Unification of HPC and Big Data Paradigms", and Madrid Regional Government, CABAHLA-CM (ConvergenciA Big dAta-Hpc: de Los sensores a las Aplicaciones) grant number S2018/TCS-4423.

### PUBLISHED AND SUBMITTED CONTENT

Publications and research contributions from the author included as part of this thesis:

- Plácido Fernández et al. «Parallelizing and Optimizing LHCb-Kalman for Intel Xeon Phi KNL Processors.» In: 2018 26th Euromicro International Conference on Parallel, Distributed and Networkbased Processing (PDP). IEEE. 2018, pp. 741–750. DOI: 10.1109/PDP2018.2018.00121

- This publication is wholly included in this thesis in Chapter 6.

- The material from this source included in this thesis is not singled out with typographic means and references.

- Placido Fernandez Declara et al. «A parallel-computing algorithm for high-energy physics particle tracking and decoding using GPU architectures.» In: *IEEE Access* 7 (2019), pp. 91612–91626. ISSN: 2169-3536. DOI: 10.1109/ACCESS.2019.2927261

- This publication is wholly included in this thesis in Chapter 7.

- The material from this source included in this thesis is not singled out with typographic means and references.

- Placido Fernandez Declara and J. Daniel Garcia. «Compass SPMD: a SPMD vectorized tracking algorithm.» 2020. Accepted for publication at CHEP 2019 Proceedings, Adelaide, Australia

- This publication is partly included in this thesis in Chapter 8.

- The material from this source included in this thesis is not singled out with typographic means and references.

the work of this thesis is presented here:

A list of publications and research contributions produced during

### **Publications:**

- Plácido Fernández et al. «Parallelizing and Optimizing LHCb-Kalman for Intel Xeon Phi KNL Processors.» In: 2018 26th Euromicro International Conference on Parallel, Distributed and Networkbased Processing (PDP). IEEE. 2018, pp. 741–750. DOI: 10.1109/PDP2018.2018.00121

- Placido Fernandez Declara et al. «A parallel-computing algorithm for high-energy physics particle tracking and decoding using GPU architectures.» In: *IEEE Access* 7 (2019), pp. 91612–91626. ISSN: 2169-3536. DOI: 10.1109/ACCESS.2019.2927261

- Placido Fernandez Declara and J. Daniel Garcia. «Compass SPMD: a SPMD vectorized tracking algorithm.» 2020. Accepted for publication at CHEP 2019 Proceedings, Adelaide, Australia

- Roel Aaij et al. «Allen: A High-Level Trigger on GPUs for LHCb.»

In: Computing and Software for Big Science 4.7 (2020). DOI: 10.

1007/s41781-020-00039-7

## Posters:

- Placido Fernandez Declara. «CompassUT: study of a GPU track reconstruction for LHCb upgrades.» 2019. URL: https://cds. cern.ch/record/2665033. Poster presented at Winter LHCC sessions, CERN, Switzerland

- Placido Fernandez Declara. «Compass SPMD: a SPMD vectorized tracking algorithm.» 2019. URL: https://cds.cern.ch/record/2699802. Poster presented at CHEP 2019, Adelaide, Australia

# Talks at international conferences:

Placido Fernandez Declara. Fast Kalman Filtering: new approaches for the LHCb upgrade. Tech. rep. 2018. URL: http://cds.cern.ch/ record/2631784

### Technical reports:

■ LHCb Collaboration. *LHCb Upgrade GPU High Level Trigger Technical Design Report*. Tech. rep. CERN-LHCC-2020-006. LHCB-TDR-021. Geneva: CERN, 2020. URL: https://cds.cern.ch/record/2717938

I am also a co-author in a number of LHCb related papers. The full list can be found at:

■ Placido Fernandez Declara. *Google Scholar profile*. https://scholar.google.com/citations?user=Ygkq\_7YAAAAJ. 2020

Particle track reconstruction in high-energy physics is used for purposes that include simulation, particle analysis, and particle collision filtering and recording. The LHCb experiment at CERN is undergoing an upgrade where improvements are being applied to the detectors, hardware and software. One of the main changes of this upgrade includes the removal of the "hardware filter" which used custom electronics to filter particle collisions, and its substitute: the "software filter". This new filter is composed of commodity hardware which must be able to process a data rate of 40 Tb per second in real-time. Different architectures are being considered to achieve this goal, and the software used to compute it must be optimized and improved to achieve the target data throughput. This software filter is used to reconstruct particle collisions, also known as *events*, including the trajectories of the resulting particles, which later are analyzed and used to help explain problems like the matter-antimatter asymmetry.

This thesis explores different opportunities with multi and manycore architectures, to improve the throughput processing of particle collisions, and the maintainability and improvement of the source code used for it.

The Kalman filter algorithm is widely used in high-energy physics for particle reconstruction, and the Intel Xeon Phi KNL processor offers a many-core x86 architecture that is well suited for parallel workloads. Performance and maintainability improvements are discussed, where optimization are targeted towards the Intel Xeon Phi processor.

GPU architectures are a good fit for high-energy physics workloads, where its highly parallel architecture can benefit the throughput processing of it. A GPU framework for event filtering is discussed, in particular the optimizations and changes implemented to a tracking algorithm to deliver high-throughput.

Finally vectorization opportunities for CPUs are explored by using data-oriented algorithms and constructs that benefit the vector units found in x86 processors. A SPMD compiler that resembles programming for GPUs is used to improve the readability and performance of these algorithms.

La reconstrucción de trayectorias en física de partículas se usa con distintos fines entre los que se incluyen la simulación, el análisis y el filtrado y recogida de las colisiones entre protones. El experimento LHCb del CERN se encuentra en pleno proceso de actualización en el que cambios y mejoras serán aplicadas a los detectores, los procesadores y el software. Uno de los principales cambios incluye la eliminación del "filtro hardware" basado en circuitos integrados específicos para estas aplicaciones, por un "filtro software". Este nuevo filtro está compuesto por procesadores de distintas arquitecturas que deben ser capaces de procesar un ratio de datos de 40 Tb por segundo, en tiempo real. Distintas arquitecturas están siendo consideradas para alcanzar este objetivo, y el software utilizado para procesarlo debe ser optimizado y mejorado para conseguir alacanzar el objetivo de rendimiento de procesamiento de datos. Este filtro basado en software es usado para reconstruir las colisiones entre partículas, también conocidas como eventos, lo que incluye las trayectorias que se producen tras la colisión entre protones. Estas son procesadas y analizadas posteriormente, lo que ayuda a entender y explicar problemas como la asimetría entre materia y antimateria.

En esta tesis se exploran las potenciales oportunidades que ofrecen las arquitecturas con múltiples núcleos de procesamiento para mejorar el rendimiento al procesar las colisiones entre partículas y el mantenimiento y mejora del código fuente usado para ello. El algoritmo filtro de Kalman es ampliamente utilizado en física de partículas para la reconstrucción de partículas, y el procesador Intel Xeon Phi KNL ofrece una arquitectura x86 con múltiples núcleos que está bien adaptada a cargas de trabajo paralelas.

Las arquitecturas GPU se adaptan bien a los problemas encontrados en física de partículas, donde su arquitectura masivamente paralela puede beneficiar el rendimiento de procesado. En esta tesis se discute un framework software basado en GPUs para filtrado de eventos, en particular se discuten las optimizaciones y cambios implementados para un algoritmo de reconstrucción para conseguir un alto rendimiento.

Finalmente se exploran las oportunidades que presenta la vectorización en CPUs utilizando algoritmos orientados a datos y estructuras que mejoran las unidades de vectorización en los procesadores x86. Un compilador de modelo SPMD que utiliza un modelo similar al utilizado con GPUs, se utiliza para mejorar la legibilidad y rendimiento de los algoritmos.

# CONTENTS

| I THE LHCB EXPERIMENT                                  |          |

|--------------------------------------------------------|----------|

| 1 INTRODUCTION                                         | 3        |

| 1.1 Motivation                                         | 5        |

| 1.2 Objectives                                         | 6        |

| 1.3 Structure of the document                          | 6        |

| 2 LHCB EXPERIMENT                                      | 9        |

| 2.1 Tracking system                                    | 10       |

| 2.1.1 VELO                                             | 10       |

| 2.1.2 UT                                               | 11       |

| 2.1.3 SciFi                                            | 13       |

| 2.2 Data acquisition system                            | 14       |

| 2.3 High Level Trigger                                 | 16       |

| 2.4 Summary                                            | 18       |

| 3 LHCB SOFTWARE AND COMPUTING                          | 19       |

| 3.1 LHCb software framework. Gaudi                     | 19       |

| 3.2 HLT1 GPU Allen framework                           | 20       |

| 3.3 Worldwide LHC Computing Grid                       | 22       |

| 3.4 Summary                                            | 24       |

| 4 LHCB TRACK RECONSTRUCTION                            | 25       |

| 4.1 Track reconstruction and pattern recognition       | 27       |

| 4.2 Track types and subdetector tracking               | 30       |

| 4.3 Physics efficiency                                 | 33       |

| 4.4 Kalman filtering                                   | 35       |

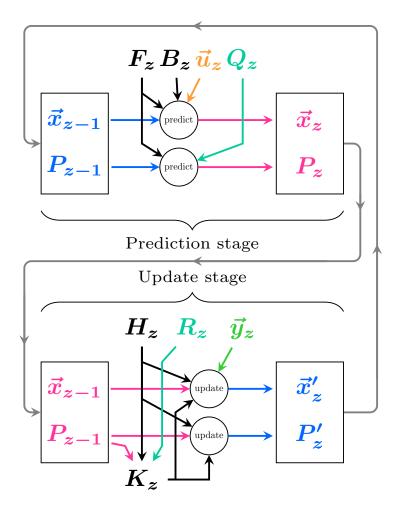

| 4.4.1 Predict stage                                    | 36       |

| 4.4.2 Update stage                                     | 37       |

| 4.5 Summary                                            | 39       |

| II PARALLEL COMPUTING                                  |          |

| 5 PARALLEL COMPUTING                                   | 12       |

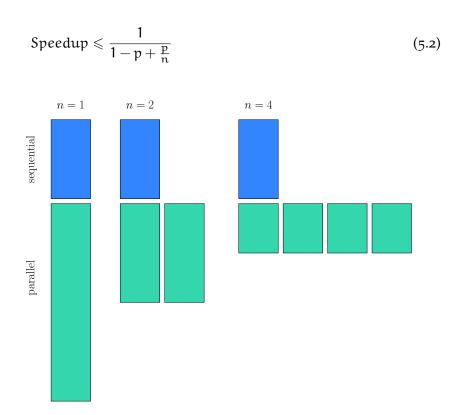

| 5.1 Speedup and scalability                            | 43       |

| 5.2 Parallel architectures                             | 44       |

| 5.2.1 Memory                                           | 47<br>50 |

| 5.2.2 Accelerators                                     | 52       |

| 5.3 Summary                                            | 56       |

|                                                        |          |

| III PARTICLE TRACKING IN HIGH-ENERGY PHYSICS           |          |

| 6 KALMAN FILTER OPTIMIZATION FOR HEP WORKLOADS         | 61       |

| 6.1 SMT multi-thread Kalman filter for Intel Xeon Phi  | 61       |

| 6.1.1 Predict-Update pipeline                          | 68       |

| 6.1.2 Four-stage track sections pipeline               | 70       |

| 6.1.3 Forward-backwards-smoother pipeline              | 73       |

| 6.1.4 Closing for the SMT multi-threaded Kalman filter | 76       |

| 6.2 Pattern based LHCb-Kalman for the Intel KNL           | 77  |

|-----------------------------------------------------------|-----|

| 6.2.1 Generic parallel patterns                           | 78  |

| 6.2.2 Parallel patterns for the Kalman filter             | 79  |

| 6.3 Summary                                               | 90  |

| 7 HEP PARTICLE TRACKING WITH GPU ARCHITECTURES            | 93  |

| 7.1 GPUs in real-time, high-throughput scientific fields  | 94  |

| 7.2 GPU framework for HLT1                                | 95  |

| 7.3 UT particle reconstruction                            | 96  |

| 7.4 UT decoding                                           | 98  |

| 7.5 Compass tracking algorithm                            | 101 |

| 7.5.1 Search UT windows                                   | 101 |

| 7.5.2 Tracklet finding                                    | 104 |

| 7.5.3 CPU implementation                                  | 106 |

| 7.6 Experimental evaluation                               | 107 |

| 7.6.1 Experimental setup                                  | 107 |

| 7.6.2 Compass tracking physics performance and throughput | 107 |

| 7.6.3 UT decoding and tracking performance                | 112 |

| 7.7 Summary                                               | 115 |

| 8 VECTORIZED SPMD ALGORITHMS                              | 117 |

| 8.1 Intel Implicit SPMD Program Compiler                  | 118 |

| 8.2 Adapting Allen for ISPC algorithms                    | 121 |

| 8.3 SPMD tracking algorithms in Allen                     | 124 |

| 8.4 Evaluation                                            | 131 |

| 8.5 Summary                                               | 133 |

| IV CONCLUSIONS                                            |     |

| 9 CONCLUSIONS AND FUTURE WORK                             | 137 |

| 9.1 Summary                                               | 137 |

| 9.2 Dissemination                                         | 141 |

| 9.3 Funding                                               | 142 |

| 9.4 Future directions                                     | 142 |

| BIBLIOGRAPHY                                              | 145 |

# LIST OF FIGURES

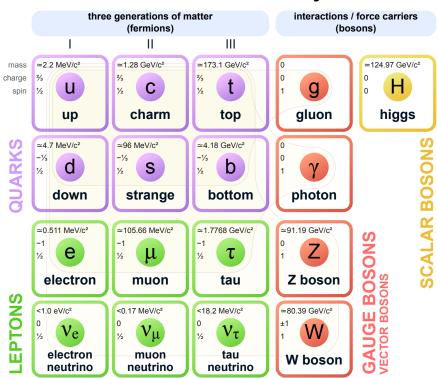

| Figure 1.1  | The Standard Model or particle physics. Image     |          |

|-------------|---------------------------------------------------|----------|

| O           | from [105]                                        | 3        |

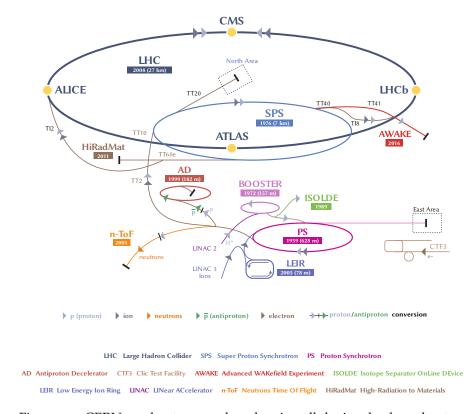

| Figure 1.2  | CERN accelerator complex, showing all the         | ,        |

| O           | involved accelerators that push the particles     |          |

|             | speed and energy to be injected in the LHC.       |          |

|             | Image from [106]                                  | 4        |

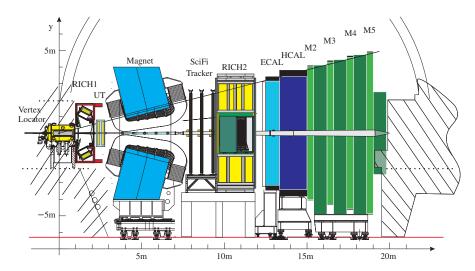

| Figure 2.1  | Schematic view of LHCb upgrade experiment.        |          |

| O           | Image from [88]                                   | 10       |

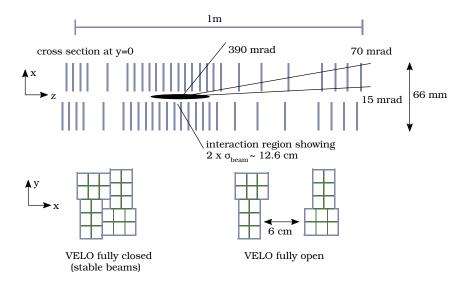

| Figure 2.2  | Velo subdetector for the upgrade in schematic     |          |

| O           | view. Image from [29]                             | 11       |

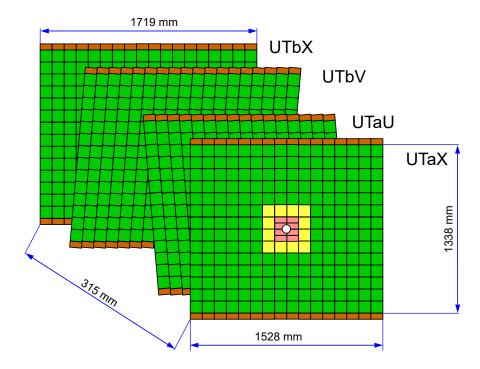

| Figure 2.3  | The four UT planes are presented in this figure.  |          |

| 0 3         | Image from [88]                                   | 12       |

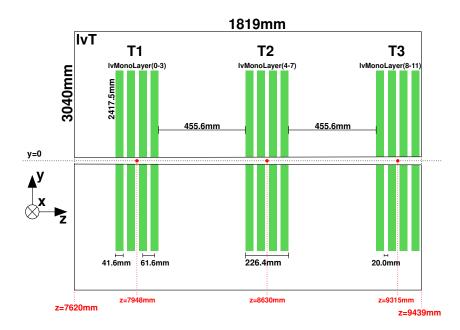

| Figure 2.4  | Arrangement of the SciFi layers. Image from [88]  | 13       |

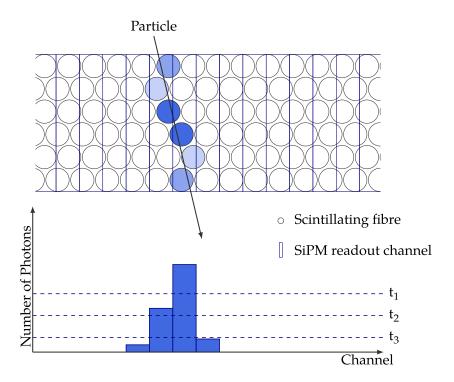

| Figure 2.5  | A particle leaves an energy deposit. Image        |          |

|             | from [108]                                        | 14       |

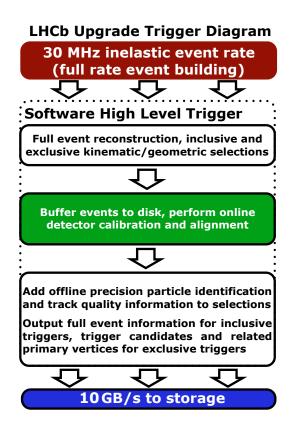

| Figure 2.6  | Run 3 trigger. Image from [118]                   | 15       |

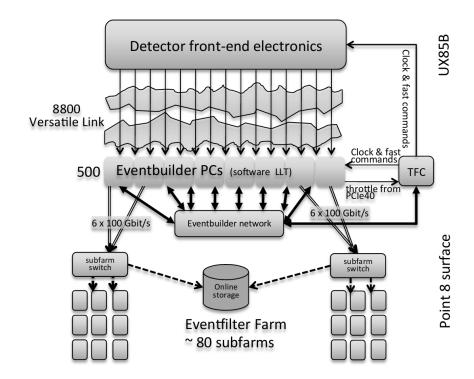

| Figure 2.7  | Layout of LHCb DAQ. Image from [42]               | 16       |

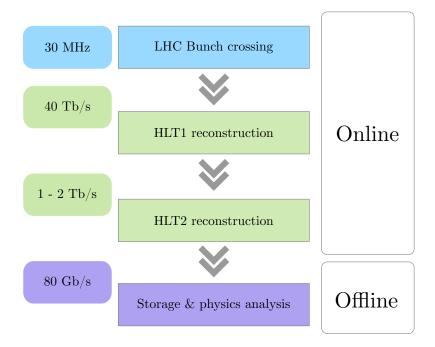

| Figure 2.8  | From LHC bunch crossing rate to analysis          | 17       |

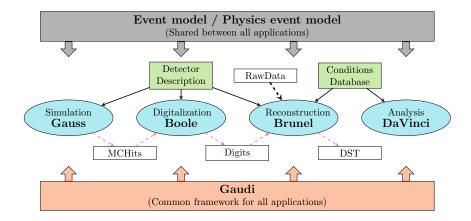

| Figure 3.1  | LHCb software applications based on Gaudi         | -/       |

|             | framework                                         | 20       |

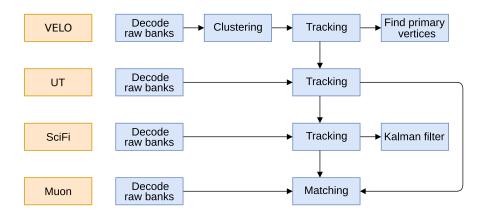

| Figure 3.2  | Algorithms run in HLT1                            | 21       |

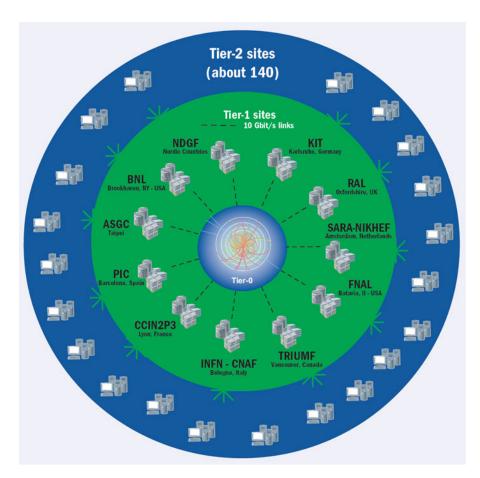

| Figure 3.3  | WLCG Tiers. Image from [98]                       | 23       |

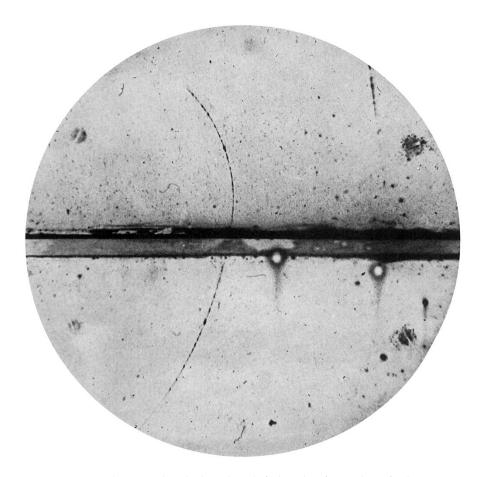

| Figure 4.1  | Track in a cloud chamber left by the first iden-  |          |

|             | tified positron. Image from [7]                   | 25       |

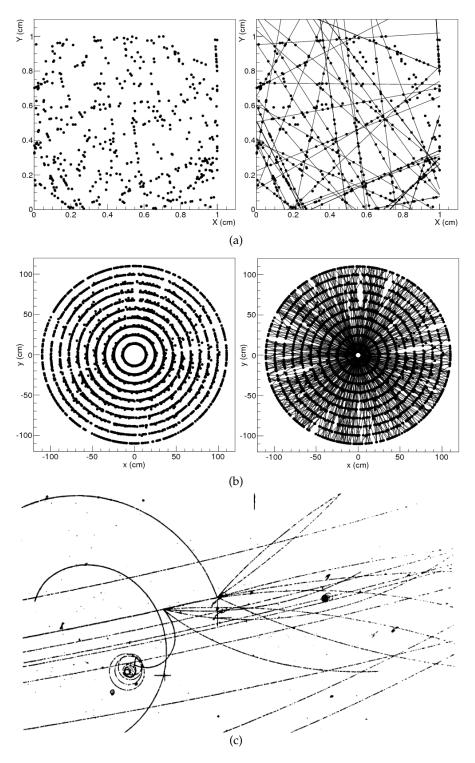

| Figure 4.2  | Various track reconstruction problems. (a) Cross- |          |

| 118410 4.2  | ing tracks in straight lines. (b) Curved tracks   |          |

|             | reconstruction. (c) Bubble chamber reconstruc-    |          |

|             | tion. Images from [73] and [12]                   | 26       |

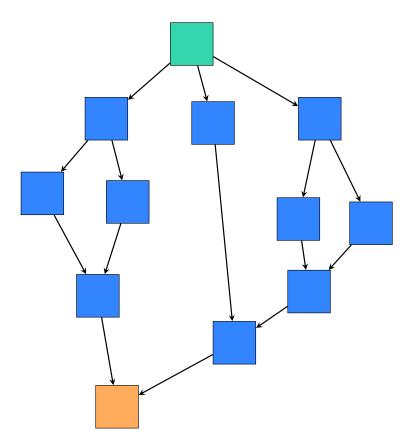

| Figure 4.3  | Global method, tree search. Image from [97] .     | 28       |

| Figure 4.4  | Histogramming with hits in a track. Image         |          |

| 1.90.10 4.4 | from [97]                                         | 29       |

| Figure 4.5  | Two seeding techniques compared side by side.     | -,       |

| 118410 4.7  | Image from [97]                                   | 29       |

| Figure 4.6  | LHCb magnetic field influence and track types.    | -9       |

| 118416 4.0  | Image from [39]                                   | 21       |

| Figure 4.7  | Track multiplicity. Image from [53]               | 31<br>32 |

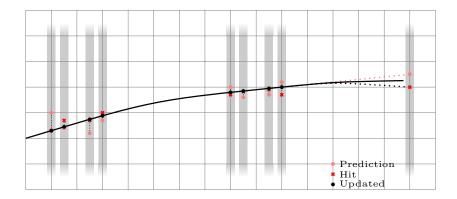

| Figure 4.8  | Kalman predict stage track representation         | 37       |

| Figure 4.9  | Kalman update stage track representation          | 38       |

| Figure 4.10 | Kalman predict and update stages relationship     | 39       |

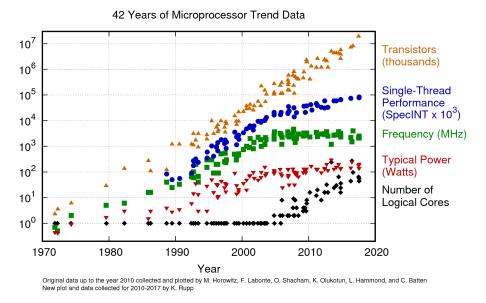

| Figure 5.1  | Microprocessor trend over the years. Image        | 99       |

| 1 15010 5.1 | from [40=]                                        |          |

| Figure 5.2  | Amdahl's law representation                             | 45         |

|-------------|---------------------------------------------------------|------------|

| Figure 5.3  | Gustafson-Barsis' law representation                    | 46         |

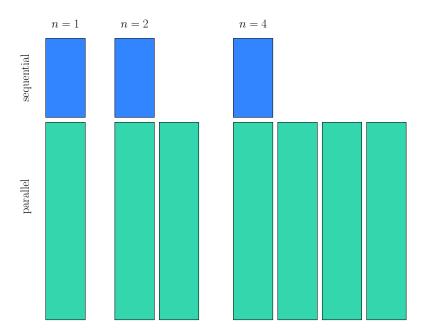

| Figure 5.4  | Work-span model representation                          | 47         |

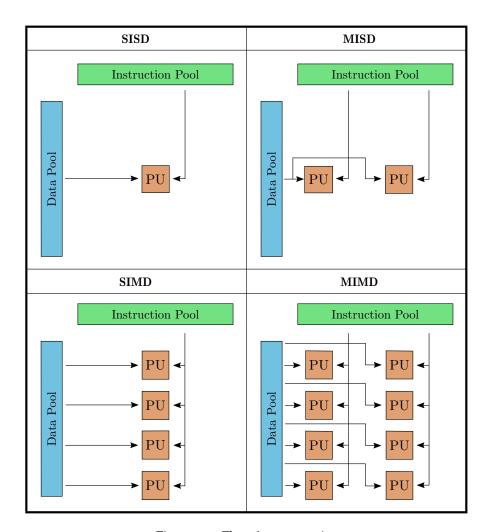

| Figure 5.5  | Flynn's taxonomies                                      | 48         |

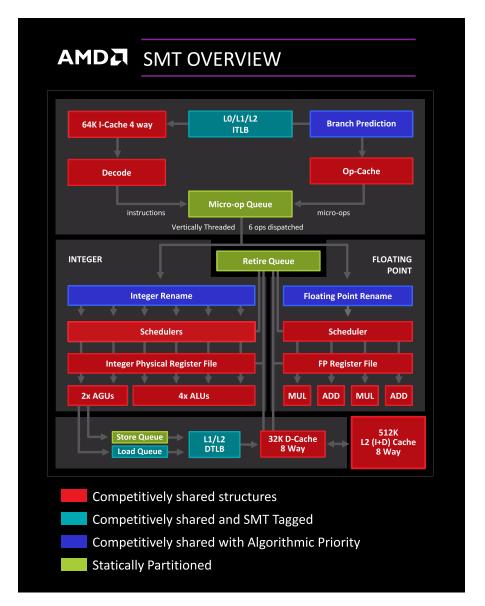

| Figure 5.6  | AMD implementation of SMT in Zen microar-               |            |

|             | chitecture. Image from [34]                             | 50         |

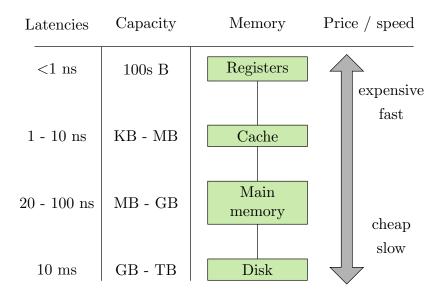

| Figure 5.7  | Memory hierarchy and its latencies                      | 51         |

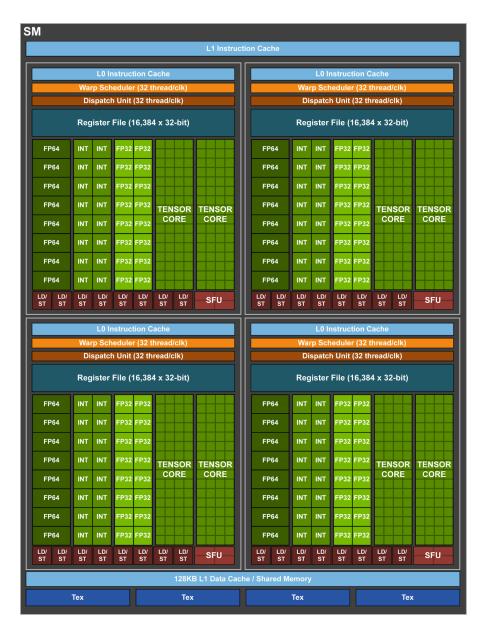

| Figure 5.8  | NVIDIA V100 Full GPU. Image from [110]                  | 53         |

| Figure 5.9  | NVIDIA V100 SM. Image from [110]                        | 54         |

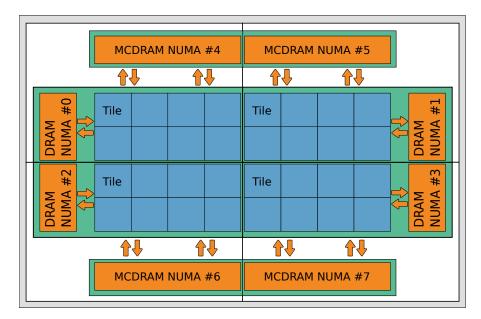

| Figure 5.10 | Intel Xeon Phi Knights Landing SNC-4 cluster            |            |

| Diagram 6 a | mode                                                    | 56         |

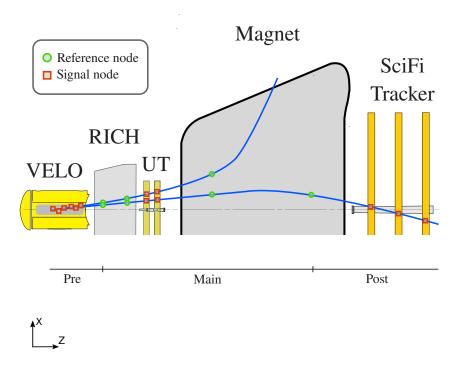

| Figure 6.1  | Reference hits and signal hits with sections of a track | 63         |

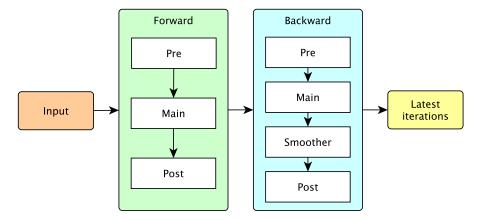

| Figure 6.2  | Kalman filter overall steps, with the forward,          |            |

| O           | backward and smoother, each with various pre-           |            |

|             | dict and update steps                                   | 64         |

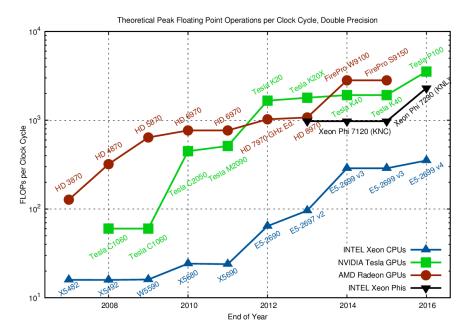

| Figure 6.3  | Intel Xeon Phi, Intel Xeon, NVIDIA Tesla and            |            |

| 0 9         | AMD Radeon architectures FLOPS compared.                |            |

|             | Image from [126]                                        | 65         |

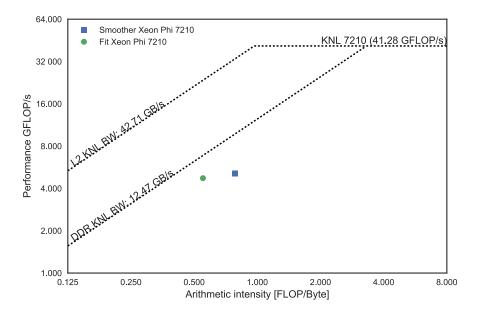

| Figure 6.4  | Intel Xeon Phi roofline plot. Image from [115]          | 66         |

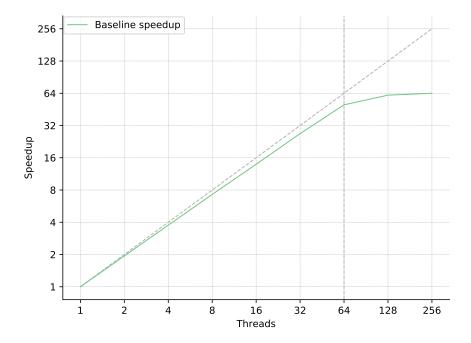

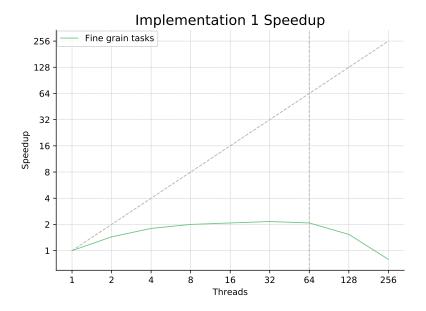

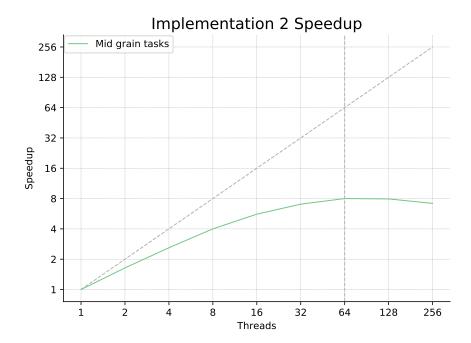

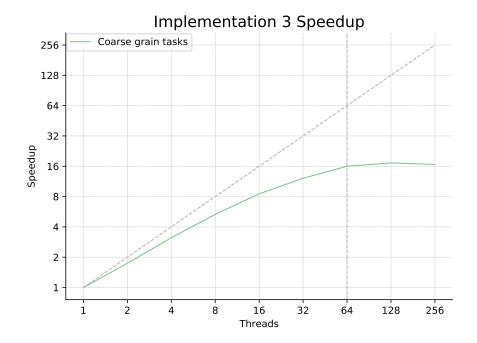

| Figure 6.5  | Intel Xeon Phi - Kalman filter scalability plot         | 67         |

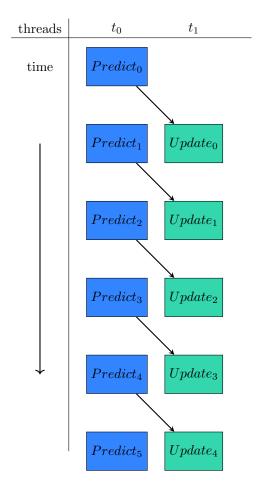

| Figure 6.6  | Predict - Update pipeline                               | 68         |

| Figure 6.7  | Predict - Update parallelization speedup                | 69         |

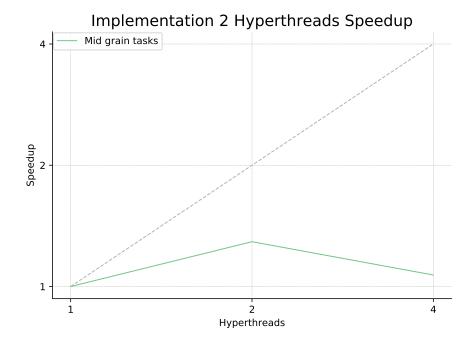

| Figure 6.8  | Predict - Update parallelization speedup in one         |            |

| O           | core                                                    | 70         |

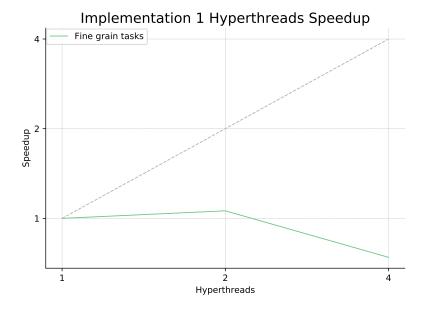

| Figure 6.9  | Predict - Update parallelization overhead. X            |            |

| 9           | axis indicates time; Y axis indicates different         |            |

|             | threads                                                 | 70         |

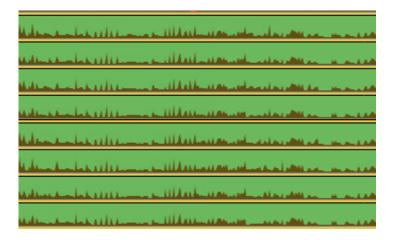

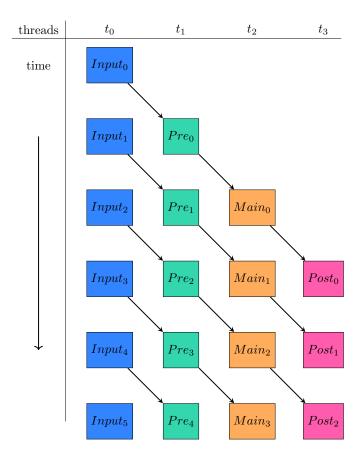

| Figure 6.10 | Four-stage pipeline                                     | 71         |

| Figure 6.11 | Four-stage parallelization speedup with input,          |            |

| G           | pre, main and post stages                               | 72         |

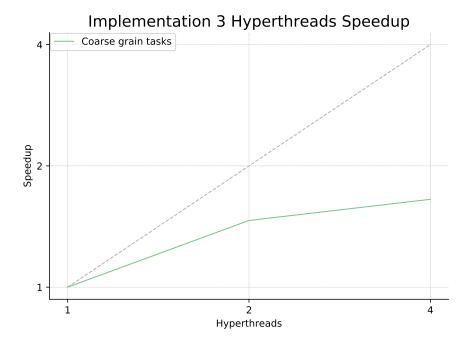

| Figure 6.12 | Four-stage parallelization speedup in one core          |            |

|             | with input, pre, main and post stages                   | 73         |

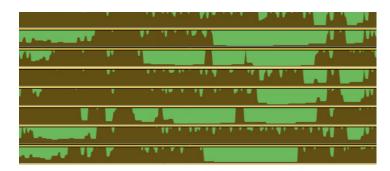

| Figure 6.13 | Four-stage parallelization overhead for various         |            |

|             | threads with input, pre, main and post stages.          |            |

|             | X axis indicates time; Y axis indicates different       |            |

|             | threads                                                 | 73         |

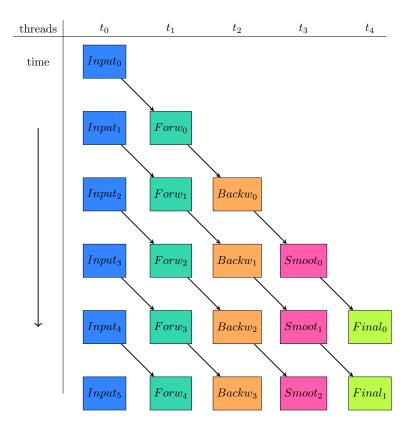

| Figure 6.14 | Forward-Backwards-Smoother pipeline                     | 74         |

| Figure 6.15 | Predict - Update parallelization speedup with           |            |

| -           | Input, Forward, Backwards, Smoother and Fi-             |            |

|             | nal steps stages                                        | <b>7</b> 5 |

| Figure 6.16 | Predict - Update parallelization speedup in one         |            |

| O           | core with Input, Forward, Backwards, Smoother           |            |

|             | and Final steps stages                                  | 75         |

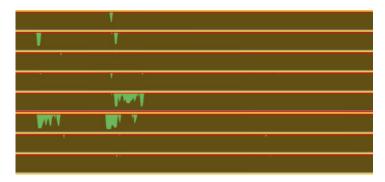

| Figure 6.17 | Predict - Update parallelization overhead in one      |    |

|-------------|-------------------------------------------------------|----|

|             | core with Input, Forward, Backwards, Smoother         |    |

|             | and Final steps stages. X axis indicates time; Y      |    |

|             | axis indicates different threads                      | 76 |

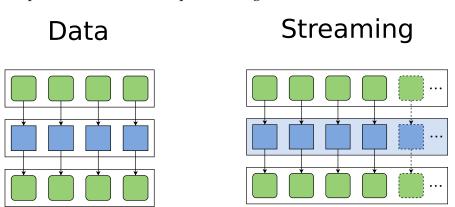

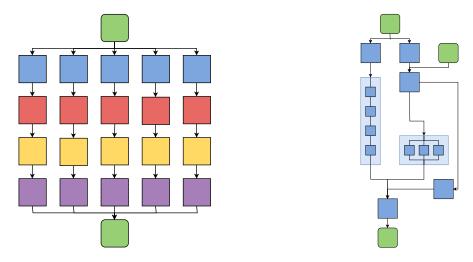

| Figure 6.18 | Data and streaming patterns represented               | 78 |

| Figure 6.19 | Parallel patterns composition and nesting             | 79 |

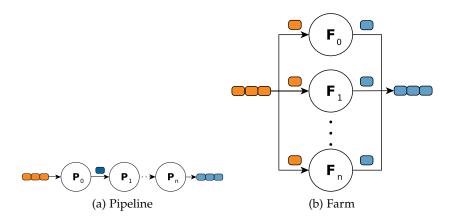

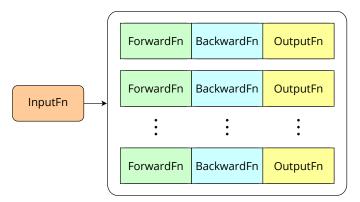

| Figure 6.20 | pipeline and farm pattern diagrams                    | 80 |

| Figure 6.21 | Phases of the Cross-Kalman algorithm. Each            |    |

| O           | phase can be decomposed in logical steps to           |    |

|             | get more fine-grained parallelism. The arrows         |    |

|             | show the order in which the phases and steps          |    |

|             | must processed                                        | 81 |

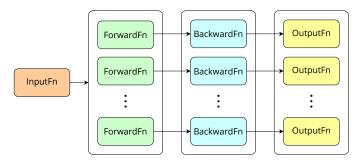

| Figure 6.22 | CK-pipeline                                           | 82 |

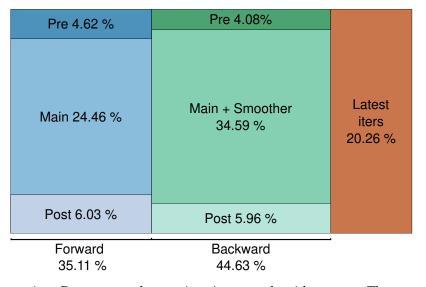

| Figure 6.23 | Percentage of execution time per algorithm            |    |

| 0           | stage. The overall time is roughly split into         |    |

|             | three parts, forward, backward and latest itera-      |    |

|             | tions. The former two are dominated by the            |    |

|             | main iterations.                                      | 82 |

| Figure 6.24 | CK-farm                                               | 83 |

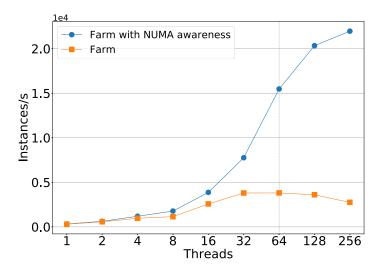

| Figure 6.25 | GrPPI with and without NUMA awareness                 |    |

| 0           | for the CK-farm pattern. Introducing NUMA             |    |

|             | awareness has a strong impact on throughput           |    |

|             | on the Intel Knights Landing platform                 | 86 |

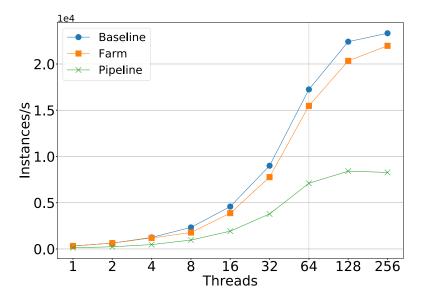

| Figure 6.26 | Throughput comparison for baseline, CK-farm           |    |

|             | and CK-pipeline                                       | 87 |

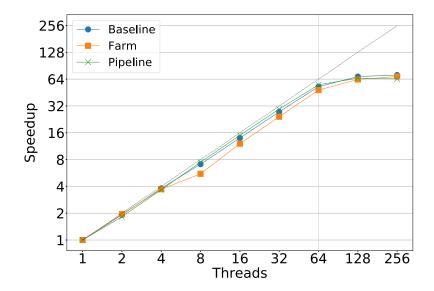

| Figure 6.27 | Scalability comparison for baseline, CK-farm          |    |

|             | and CK-pipeline                                       | 88 |

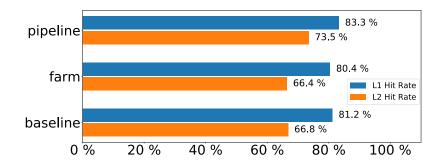

| Figure 6.28 | Comparison of L1 & L2 cache hit rates between         |    |

|             | the baseline, CK-farm and CK-pipeline pattern         |    |

|             | implementations. The <i>pipeline</i> pattern has a 7% |    |

|             | higher L2 cache hit rate than the other imple-        |    |

|             | mentations                                            | 88 |

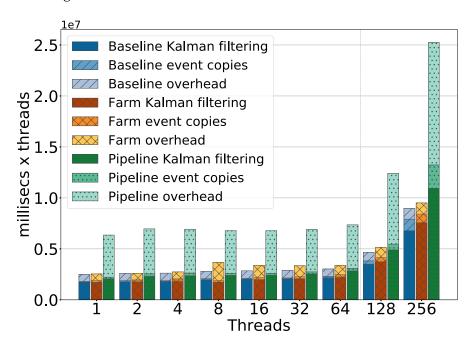

| Figure 6.29 | A decomposition of the wall-clock times into          |    |

|             | Kalman filter processing, data copies and frame-      |    |

|             | work overhead. The framework overhead in              |    |

|             | CK-pipeline is substantially higher than the base-    |    |

|             | line or CK-farm implementation                        | 89 |

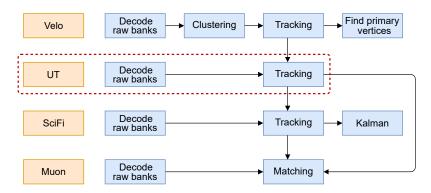

| Figure 7.1  | Complete High Level Trigger 1 sequence of             |    |

|             | algorithms at LHCb. The UT algorithms de-             |    |

|             | scribed in this chapter (dotted lines) are high-      |    |

|             | lighted. UT is the second tracking sub-detector       |    |

|             | in the chain of algorithms, and it receives input     |    |

|             | from the UT raw banks and the VELO tracks.            |    |

|             | UT outputs reconstructed tracks for other sub-        |    |

|             | detectors                                             | 97 |

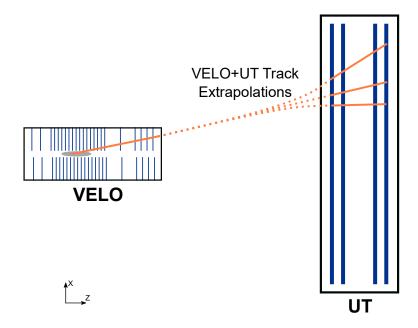

| Figure 7.2 | VELO track extrapolation to UT hits. A VELO        |     |

|------------|----------------------------------------------------|-----|

|            | track can be associated to various UT hits, where  |     |

|            | the UT track extrapolation does not necessarily    |     |

|            | follow a straight line. This leads to high com-    |     |

|            | binatorics between the hits in the four panels,    |     |

|            | holding the main complexity of the algorithm.      | 98  |

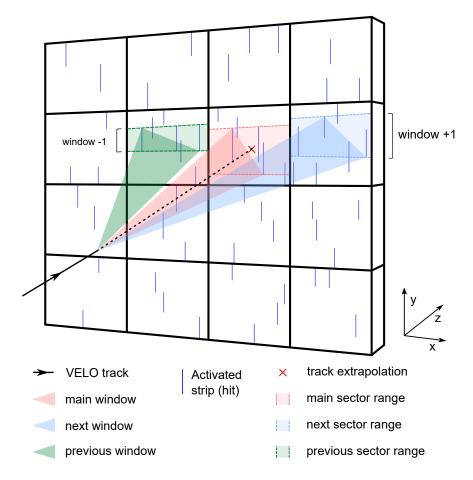

| Figure 7.3 | UT window ranges: representation of a VELO         |     |

| 0 75       | track extrapolation to a sector. Window ranges     |     |

|            | are set for the sector and its neighbours. Several |     |

|            | hits lie within the range of the windows, which    |     |

|            | are considered for UT tracking                     | 102 |

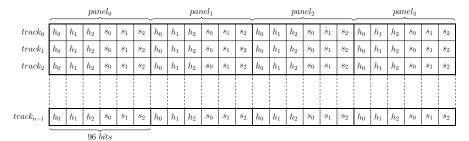

| Figure 7.4 | Memory layout of window ranges. A beginning        | 102 |

| 11guic /.4 | hit, and a size are stored per window range,       |     |

|            | using 16 bits for each element. In this figure, a  |     |

|            | -                                                  |     |

|            | 3 sectors window ranges is shown, where each       |     |

|            | elements has a size of 16 bits, making it a total  |     |

| г.         | of 96 bits for all the elements of a panel         | 103 |

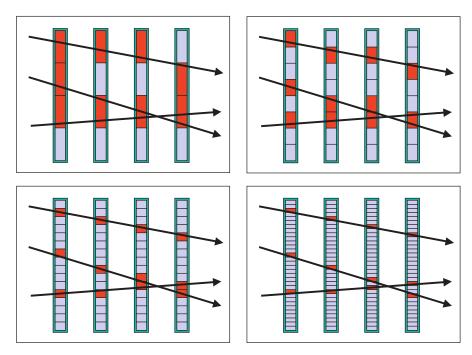

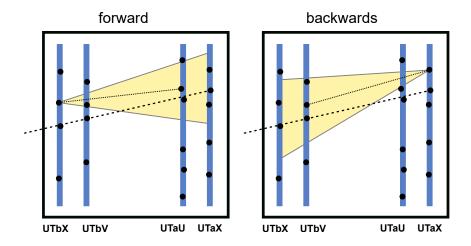

| Figure 7.5 | Tracklet finding kernel. Combinatorics between     |     |

|            | all 4 panels when searching for hits candidates    |     |

|            | to form a tracklet are shown. The fine dotted      |     |

|            | line represents the slope between the two first    |     |

|            | hits found in the first and third panels. The      |     |

|            | coarse dotted line represents the VELO track       |     |

|            | slope. A tolerance window defined by them is       |     |

|            | calculated to search for a tracklet                | 105 |

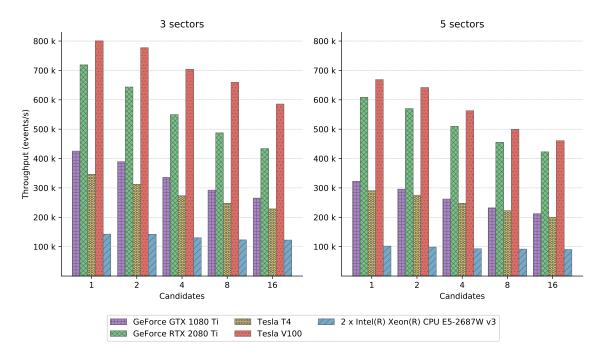

| Figure 7.6 | 3 vs 5 sectors <i>Compass</i> tracking comparison. |     |

|            | Throughput comparison between the two con-         |     |

|            | sumer grade GPUs, two server grade GPUs and        |     |

|            | a dual socket Intel Xeon CPU, comparing with 1     |     |

|            | to 16 number of hit candidates. The throughput     |     |

|            | shown here corresponds to running the Com-         |     |

|            | pass algorithm. The figure in the left plots the   |     |

|            | throughput when looking for hits in 3 sectors.     |     |

|            | The right figure depicts the throughput when       |     |

|            | looking for hits in 5 sectors, adding an extra     |     |

|            | neighbour sector on each side with respect to      |     |

|            | the 3 sectors case                                 | 110 |

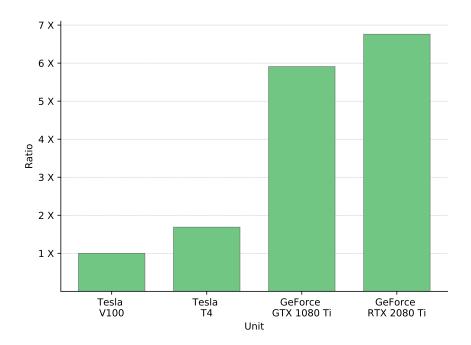

| Figure 7.7 | Price performance ratio for Compass in GPU.        |     |

| 0.0        | All prices are factored to MSRP price indicated    |     |

|            | in Table 7.2. The price performance of the 5       |     |

|            | sectors case is compared, for the best physics     |     |

|            | efficiency case with 16 candidates                 | 112 |

|            | cifferency case with to canadates                  | 112 |

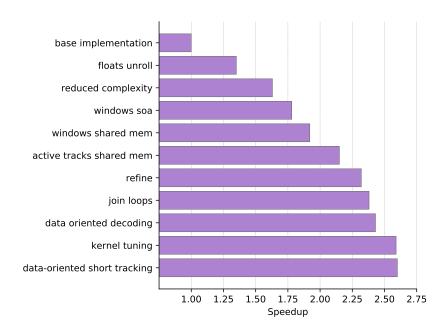

| Figure 7.8  | Incremental optimizations speedup. Speedup achieved after applying different optimizations |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

|             | to the baseline code. A maximum speedup of                                                 |  |  |  |  |  |

|             | $2.6 \times$ is achieved in the final version, compared                                    |  |  |  |  |  |

|             | to the baseline implementation. Various small                                              |  |  |  |  |  |

|             | optimizations and changes are grouped into                                                 |  |  |  |  |  |

|             | steps                                                                                      |  |  |  |  |  |

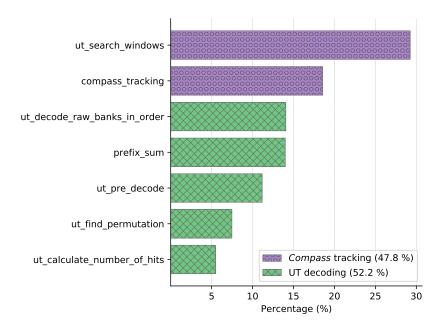

| Figure 7.9  | Kernels time contribution. Runtime distribu-                                               |  |  |  |  |  |

|             | tion of all the kernels used to compute the                                                |  |  |  |  |  |

|             | decoding and Compass algorithm. The best                                                   |  |  |  |  |  |

|             | physics efficiency case is used here, with 5 sec-                                          |  |  |  |  |  |

|             | tors and 16 candidates for the NVIDIA 2080Ti                                               |  |  |  |  |  |

|             | case                                                                                       |  |  |  |  |  |

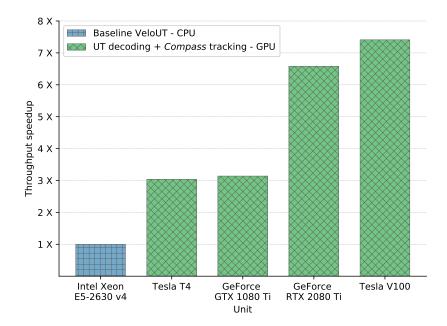

| Figure 7.10 | Basline LHCb vs GPU decoding + Compass                                                     |  |  |  |  |  |

|             | tracking throughput speedup comparison. Through-                                           |  |  |  |  |  |

|             | put speedup of the full UT chain of kernels,                                               |  |  |  |  |  |

|             | including the decoding and Compass tracking,                                               |  |  |  |  |  |

|             | compared to the baseline LHCb CPU imple-                                                   |  |  |  |  |  |

|             | mentation as stated in Section 7.10. The LHCb                                              |  |  |  |  |  |

|             | baseline (blue) is compared with the <i>Compass</i>                                        |  |  |  |  |  |

|             | over different GPUs (green)                                                                |  |  |  |  |  |

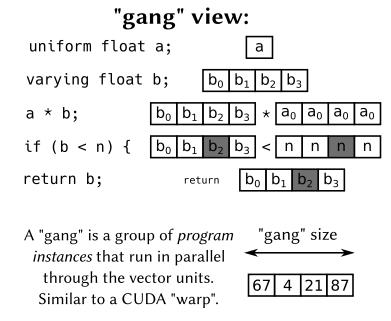

| Figure 8.1  | ISPC gangs                                                                                 |  |  |  |  |  |

| Figure 8.2  | ISPC assembly vector instructions 120                                                      |  |  |  |  |  |

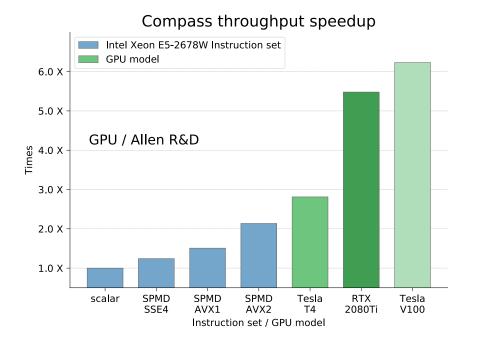

| Figure 8.3  | Performance comparison                                                                     |  |  |  |  |  |

|             |                                                                                            |  |  |  |  |  |

| LIST OF T   | ABLES                                                                                      |  |  |  |  |  |

| Table 4.1   | Physics efficiency indicators                                                              |  |  |  |  |  |

| Table 6.1   | Time spent in the producer and consumer tasks                                              |  |  |  |  |  |

|             | when using 8 threads with the GrPPI farm 90                                                |  |  |  |  |  |

| Table 7.1   | Kernel configuration for UT decoding. events_in_execution                                  |  |  |  |  |  |

|             | are the number of selected events to process,                                              |  |  |  |  |  |

|             | where array_size is defined as the events_in_execution $	imes$                             |  |  |  |  |  |

|             | 84. 84 is the number of pre-defined sectors,                                               |  |  |  |  |  |

|             | where the number 4 used in various kernels is                                              |  |  |  |  |  |

|             | the number of panels. Threads with two argu-                                               |  |  |  |  |  |

|             | ments is the kernel execution configuration for                                            |  |  |  |  |  |

|             | thread blocks and threads in a block 99                                                    |  |  |  |  |  |

| Table 7                                             | uation. Two high-end consumer graphics cards (GeForce GTX 1080Ti and GeForce RTX 2080Ti), two server-grade cards (Tesla T4 and Tesla V100), and an Intel Xeon CPU are compared. It shows the number of cores of each processor, where for the GPUs it counts the CUDA cores only (no RT cores or Tensor cores are used in the benchmarks). The MSRP (manufacturer suggested retail price) is used for each hardware unit used here. The price for a single Intel Xeon CPU is shown, whereas for the benchmarks a dual socket server with two Intel Xeon CPUs is used. This is reflected in the price performance figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 108                               |  |  |  |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

|                                                     | and VELO+UT tracks. For each type of track, the track reconstruction efficiency and track clone rate achieved are presented. The obtained fake rate for each case is also shown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 109                               |  |  |  |  |

| Table 8                                             | 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |  |  |  |  |

| Table 8                                             | binations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 121                               |  |  |  |  |

|                                                     | are identified by the $spmd_p$ prefix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 131                               |  |  |  |  |

| LISTI                                               | NGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |  |  |  |  |

| 6.1                                                 | Parallelism at phase level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 82                                |  |  |  |  |

| 6.2                                                 | TBB pipeline implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83                                |  |  |  |  |

| 6.3                                                 | Example of hwloc for CPU and NUMA affinity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                   |  |  |  |  |

| 6.4                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |  |  |  |  |

| 6.5                                                 | GRPPI interfaces for CPU and NUMA affinity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8 <sub>4</sub><br>8 <sub>5</sub>  |  |  |  |  |

| 8.1                                                 | ISPC source code sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 119                               |  |  |  |  |

| 8.2                                                 | ISPC and GCC algorithms interleaved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 122                               |  |  |  |  |

| 8.3 Memory allocation and copies change from GPU to |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |  |  |  |  |

| 8.4                                                 | Casting types for ISPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 123                               |  |  |  |  |

| 8.5                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                   |  |  |  |  |

| 8.6                                                 | o contract the state of the sta |                                   |  |  |  |  |

| 8.7                                                 | Template usage in GPU Allen framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul><li>125</li><li>126</li></ul> |  |  |  |  |

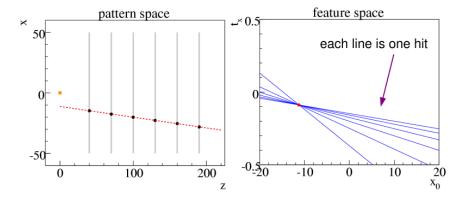

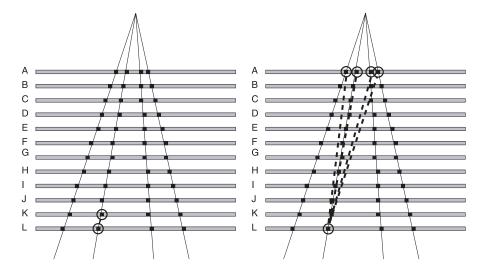

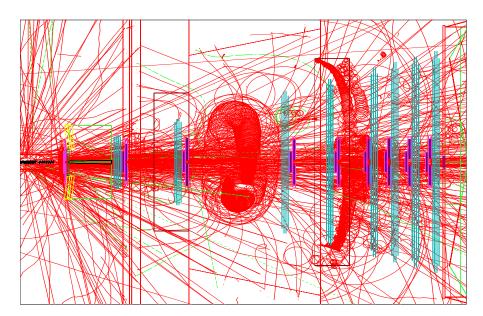

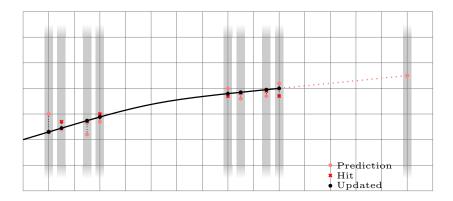

| 8.8                                                 | CUDA function for <i>host</i> and <i>device</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 126                               |  |  |  |  |