# **PROYECTO FIN DE CARRERA**

Escuela Politécnica Superior Ingeniería en Informática

Departamento de Informática

AdaptBenchmark: El benchmark adaptativo universal

> AUTOR: Antonio Díaz Ponce TUTOR: David Expósito Singh

| Título: AdaptBenchmark: El benchmark adaptativo universal                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Autor: Antonio Díaz Ponce                                                                                                                                                                                                                         |

| Tutor: David Expósito Singh                                                                                                                                                                                                                       |

| EL TRIBUNAL                                                                                                                                                                                                                                       |

| Presidente: Jesús Carretero Pérez                                                                                                                                                                                                                 |

| Vocal: Francisco Javier García Blas                                                                                                                                                                                                               |

| Secretario: Alberto Valero Gómez                                                                                                                                                                                                                  |

| Realizado el acto de defensa y lectura del Proyecto Fin de Carrera el día 12 de diciembre de 2011 en Leganés, en la Escuela Politécnica Superior de la Universidad Carlos III de Madrid, acuerda otorgarle la CALIFICACIÓN de: MATRÍCULA DE HONOR |

| VOCAL                                                                                                                                                                                                                                             |

| SECRETARIO PRESIDENTE                                                                                                                                                                                                                             |

# **AGRADECIMIENTOS**

En primer lugar quiero agradecer y dedicar la creación de este proyecto a mis padres, por ser siempre un fuerte apoyo tanto en los buenos como en los malos momentos. A mi hermano, por no ser sólo un hermano, sino el mejor amigo que podría tener; a mi familia: tíostías y primos-primas, y en especial a mis abuelos y abuelas que seguro que estarán contentos de ello.

Quiero dar las gracias a mi tutor, David Expósito, por su gran aporte a este proyecto, por la cordialidad y el buen trato durante las tutorías, por esas ideas que a mí jamás se me ocurrirían. Y por aguantarme durante tanto tiempo. Ha sido un placer trabajar contigo David.

A mis compañeros de universidad y amigos: Álvaro y Javier, con vosotros he pasado el mayor tiempo haciendo esas interminables prácticas y con vosotros he vivido momentos que jamás olvidaré, sois muy grandes. Gracias a Lidia y Roberto por ser los primeros en dar sin recibir nada a cambio y por vuestra forma de ser, no cambiéis nunca. Gracias Christian por ser uno de los compañeros más eficientes que he conocido y por ofrecer ese punto de vista siempre desconocido. Gracias Óscar y Laura por demostrar que después de la universidad no acaba todo sino que comienzan mejores momentos. A Luis por ser un gran compañero, por ofrecer constantemente ayuda y consejo, y por su humor inteligente. Gracias Córdoba por ser guía, amigo y compañero de equipo durante toda la carrera.

También quiero agradecer a mis amigos de primera por conseguir que olvide los malos momentos con sólo pasar un rato con vosotros. Gracias por estar ahí siempre proponiendo nuevas cosas.

No podría faltar en este agradecimientos mis amigos del colegio: Luis, Lorenzo y Fernando; por seguir siendo igual desde hace tanto tiempo sin dejar que nada ni nadie os cambie, siempre habéis sido esa constante que todo el mundo tiene que tener para sentirse feliz.

Por último, y no menos importante dar gracias a todos los compañeros de equipo con los que he conseguido seguir aprendiendo nuevas cosas de vosotros. Milan gracias por todo aunque estés lejos, no te olvidaremos.

Gracias a todos los que aunque no haya nombrado se sientan identificados con parte de esto.

Un abrazo fuerte.

## RESUMEN

Desde la primera aparición de las plataformas de computación, ha sido necesaria la comparación del rendimiento de los distintos productos. El término benchmark emerge a finales del siglo XIX, definido como un punto de referencia en la toma de medidas. Actualmente, este tema está más relacionado con herramientas software que evalúan el rendimiento del ordenador. Este proyecto trata sobre la definición, creación y evaluación de un conjunto de benchmarks para tomar medidas del rendimiento de los microprocesadores. Lo hemos denominado AdaptBenchmark: el benchmark adaptativo universal. Este benchmark incluye diferentes test que evalúan varias características de la arquitectura de un procesador.

En este documento explicamos la metodología que hemos seguido durante el desarrollo del AdaptBenchmark. Detallamos la estructura interna del software, que ha sido concebida para evaluar el rendimiento de modernos procesadores con varios núcleos. AdaptBenchmark mide el tiempo de ejecución y eventos internos como: fallos caché en L1 y L2, tráfico de bus o fallos TLB. Esta información es recogida utilizando contadores hardware y resumida mediante gráficas.

Para cada test desarrollamos un estudio extensivo del desarrollo de procesador así como un análisis de las interacciones entre software y el correspondiente hardware. Además, introducimos una técnica para buscar la mejor configuración en las distintas plataformas. Para ello utilizaremos dos técnicas de optimización: Simmulated Annealing y la Búsqueda N-aria. Esta última fue creada específicamente para este proyecto. Con la utilización de estas metodologías es posible adaptar el benchmark a distintos contextos hardware.

A lo largo de este proyecto, trabajaremos con dos arquitecturas diferentes: Intel Core2Duo y AMD Opteron. Y compararemos al detalle el funcionamiento de estas dos plataformas para distintas configuraciones, probando así la eficiencia de nuestra herramienta.

Palabras clave: benchmark, rendimiento, evaluación, arquitectura, microprocesador.

## **ABSTRACT**

Since the first appearance of computing platforms, it was necessary to compare the performance of different products. The term benchmark emerges at the end of 19<sup>th</sup> century, defined as a point of reference for a measurement. Nowadays, this topic is commonly related to software tools that evaluate the computer performance. This project is about the definition, creation and evaluation of a set of benchmarks for measuring the microprocessor performance. We call them AdaptBenchmark: a universal adaptive benchmark. This benchmark includes different tests that evaluate several characteristics of the processor architecture.

In this document we introduce the methodology that we have followed during the development of AdaptBenchmark. We detail the internal structure of this software, which was conceived for evaluating the performance of modern multicore processors. AdaptBenchmark measures the execution time as well as internal processor events like L1 and L2 cache misses, bus traffic or TLB misses. This information is collected using the hardware counters and then summarized in chars.

For each test we perform an extensive study of the processor performance as well as an analysis of the interactions between the software and the underlining hardware. In addition, we introduce a technique for fine-tuning the benchmark in order to find the best configuration for each platform. In order to do this, we use two optimization techniques: the Simmulated Annealing and the n-ary Search. The latter one was originally created in this project. With the use of this methodology it is possible to adapt the benchmark to different hardware contexts.

Finally, we perform the evaluation of AdaptBenchmark for two different architectures: Intel Core2Duo and AMD Opteron. We make a detailed comparison between these two platforms for different hardware configurations, proving the efficiency of our tool.

Keywords: benchmark, performance, evaluation, architecture, microprocessor.

Caminante, no hay camino, se hace camino al andar. Antonio Machado

# ÍNDICE GENERAL

| ÍNDICE GENERAL                                                 | 8  |

|----------------------------------------------------------------|----|

| 1 Introducción                                                 | 13 |

| 1.1 Motivación general                                         | 13 |

| 1.2 Objetivos del proyecto                                     | 14 |

| 1.3 Introducción de la memoria                                 | 16 |

| 2Plataforma de evaluación                                      | 17 |

| 2.1 Intel Core 2 Duo T7100                                     | 17 |

| 2.2 AMD Opteron 6168                                           | 20 |

| 2.3 Contadores hardware                                        | 22 |

| 2.4 Entorno software                                           | 25 |

| 2.4.1 OpenMP                                                   | 25 |

| 2.4.2 Librería PAPI                                            | 26 |

| 2.4.3 Prefetching                                              | 27 |

| 2.4.3.1 Prefetching Hardware, MSR-TOOLS                        | 28 |

| 2.4.3.2 Prefetching Software                                   | 31 |

| 2.4.4 Huge Pages                                               | 31 |

| 3 Benchmarks de evaluación                                     | 33 |

| 3.1 Escritura con stride                                       | 33 |

| 3.2 False sharing                                              | 36 |

| 3.3 Producto matriz-dispersa vector                            | 39 |

| 3.4 Técnica de optimización                                    | 43 |

| 3.4.1 Simmulated Annealing                                     | 43 |

| 3.4.2 Búsqueda N-aria                                          | 46 |

| 4 Experimentos                                                 | 49 |

| 4.1 Definición de parámetros de la arquitectura a evaluar      | 49 |

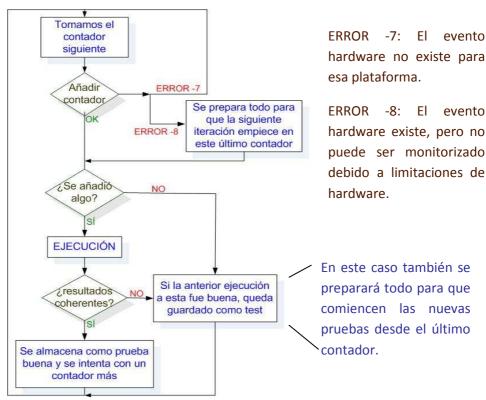

| 4.1.1 Selección dinámica de contadores                         | 50 |

| 4.2 Metodología para evaluar los parámetros de la arquitectura | 52 |

| 4.3 Metodología de análisis de los resultados                  | 54 |

| 4.4 Escritura con stride                                       | 57 |

| 4.4.1 Intel Core2Duo                                           | 57 |

| 4.4.1.1 Prefetching                                            | 61 |

| 4.4.2 AMD Opteron                                              | 64 |

| 4.4.3 Comparativa                            | 66  |

|----------------------------------------------|-----|

| 4.5 False sharing                            | 69  |

| 4.5.1 Intel Core2Duo                         | 69  |

| 4.5.1.1 Prefetching                          | 71  |

| 4.5.2 AMD Opteron                            | 73  |

| 4.5.3 Comparativa                            | 76  |

| 4.6 Producto Matriz-dispersa vector          | 78  |

| 4.6.1 Dispersión                             | 79  |

| 4.6.1.1 Intel Core2Duo                       | 81  |

| 4.6.1.2 AMD Opteron                          | 84  |

| 4.6.1.3 Comparativa                          | 85  |

| 4.6.2 Número de hilos                        | 87  |

| 4.6.2.1 Intel Core2Duo                       | 87  |

| 4.6.2.2 AMD Opteron                          | 90  |

| 4.6.2.3 Comparativa                          | 91  |

| 4.6.4 Tipos de planificación                 | 96  |

| 4.7 Huge pages                               | 98  |

| 4.8 Integración con Técnicas de optimización | 100 |

| 4.8.1 Simulated Annealing                    | 101 |

| 4.8.2 Búsqueda N-aria                        | 107 |

| 4.8.3 Comparativa                            | 109 |

| 5 Comparativa Final                          | 112 |

| 6 Planificación y presupuesto                | 116 |

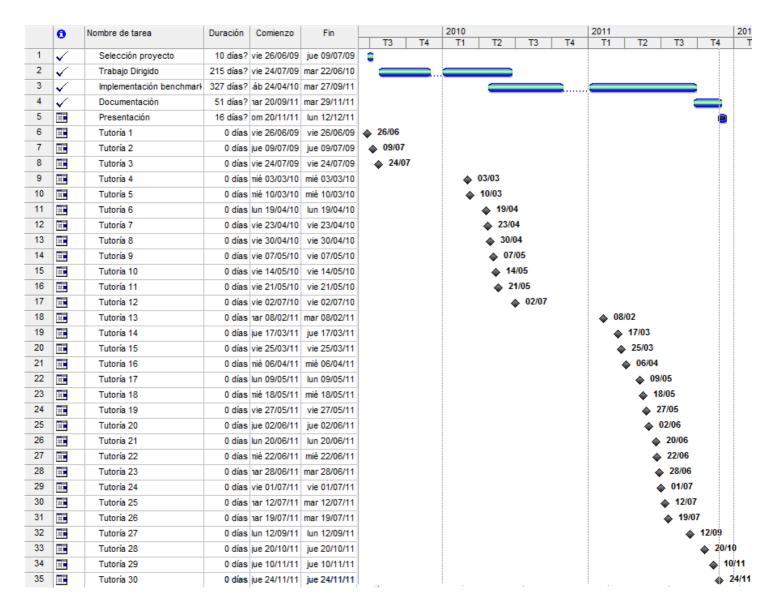

| 6.1 Planificación                            | 116 |

| 6.2 Presupuesto                              | 120 |

| 7 Conclusiones                               | 123 |

| 7.1 Líneas futuras                           | 124 |

| 8 Glosario                                   | 126 |

| 9 Referencias                                | 127 |

| Apéndice A: PAPI Guía de instalación y uso   | 130 |

| Apéndice B: Ejemplo de uso de Huge Pages     |     |

| Apéndice C: Manual de usuario                |     |

# ÍNDICE DE FIGURAS

| Figura 1: Imagen renderizada con 3DMark                                                              | 13 |

|------------------------------------------------------------------------------------------------------|----|

| Figura 2: Funciones de correspondencia directa y asociativa por conjuntos de 2 vías                  |    |

| Figura 3: Arquitectura del procesador Intel Core 2 Duo                                               | 18 |

| Figura 4: Gráfica de situación de la caché L2 en un Core 2 Duo                                       |    |

| Figura 5: Vista ampliada de un Opteron Istanbul                                                      |    |

| Figura 6: Pirámide de tipos de memoria en relación con CPU                                           | 23 |

| Figura 7: Captura del renderizador de imágenes médicas AMIDE                                         | 28 |

| Figura 8: Captura en la que la BIOS permite desactivar el prefetching hardware                       | 29 |

| Figura 9: Prefetchers dentro del Intel Core 2 Duo                                                    | 30 |

| Figura 10: Prefetchers dentro del Intel Core 2 Duo                                                   | 31 |

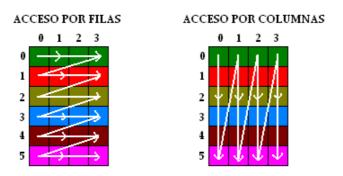

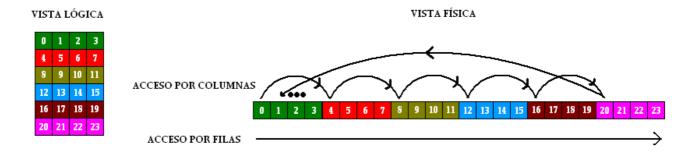

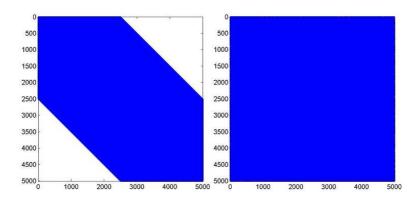

| Figura 11: Acceso a matrices por filas y por columnas                                                | 33 |

| Figura 12: Vista física de acceso por filas y por columnas                                           | 34 |

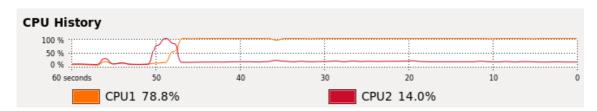

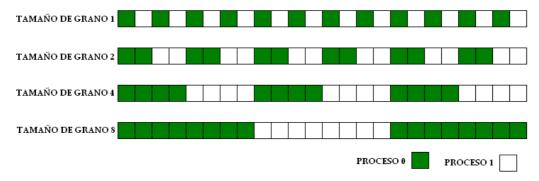

| Figura 13: Ocupación de los núcleos en la prueba escritura con stride                                | 35 |

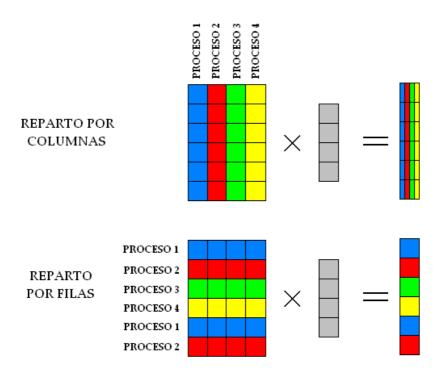

| Figura 14: Ejemplo de reparto de tareas en false sharing                                             | 36 |

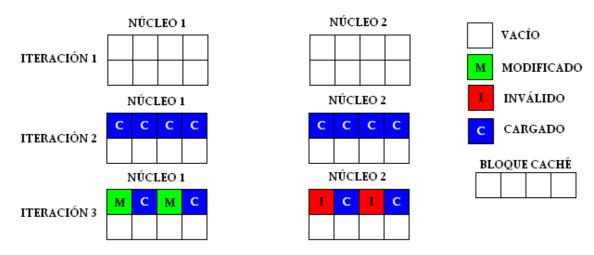

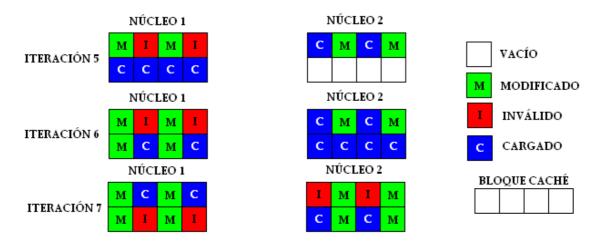

| Figura 15: Ejemplo1 traza false sharing                                                              | 37 |

| Figura 16: Ejemplo2 traza false sharing                                                              | 37 |

| Figura 17: Ocupación de los núcleos en la prueba false sharing                                       |    |

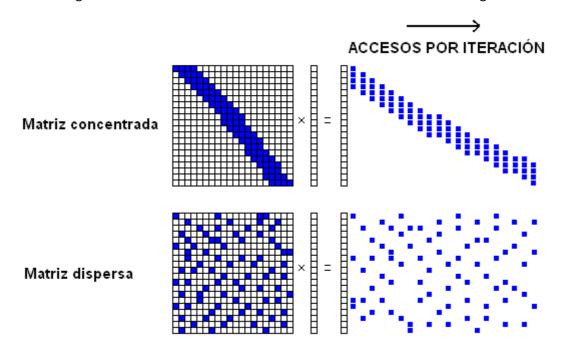

| Figura 18: Producto entre una matriz y vector                                                        |    |

| Figura 19: Matriz dispersa, comprimida triplete y CSR                                                | 39 |

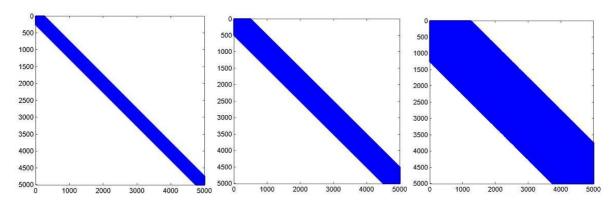

| Figura 20: Matrices con grados de dispersión 1, 2, 5, 10 y 20 respectivamente, número de filas 5000, |    |

| número de elementos por fila 500                                                                     | 41 |

| Figura 21: Reparto de la carga de producto de matriz-vector por filas y columnas                     | 42 |

| Figura 22: Ocupación de los núcleos en la prueba producto matriz-dispersa vector                     | 42 |

| Figura 23: Fórmula de cálculo de probabilidad en Simulated Annealing                                 |    |

| Figura 24: Fórmula de la constante Boltzmann                                                         |    |

| Figura 25: Explicación de Simulated Annealing                                                        |    |

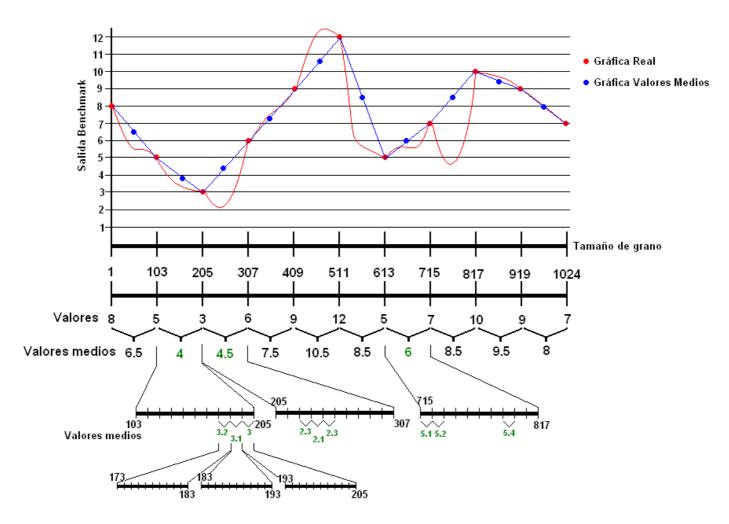

| Figura 26: Ejemplo de Búsqueda N-aria                                                                |    |

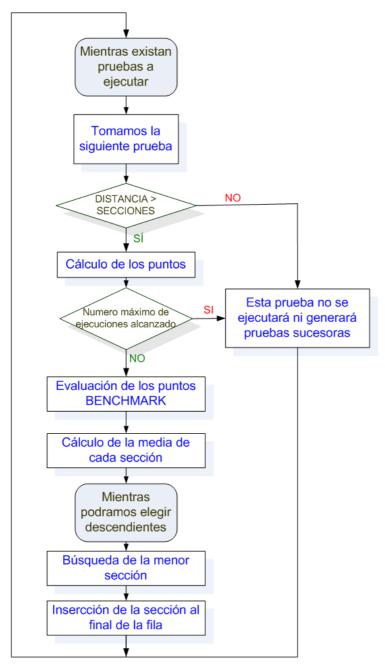

| Figura 27: Diagrama de Búsqueda N-aria                                                               |    |

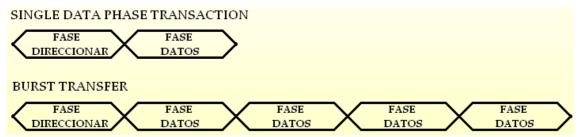

| Figura 28: Single data phase transaction vs burst transfer                                           |    |

| Figura 29: Diagrama de funcionamiento del testeador de evento                                        | 51 |

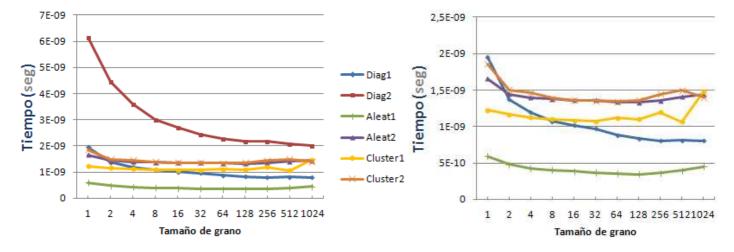

| Figura 30: Tiempos para experimentos 1 y 2 [ES][Core2Duo]                                            | 57 |

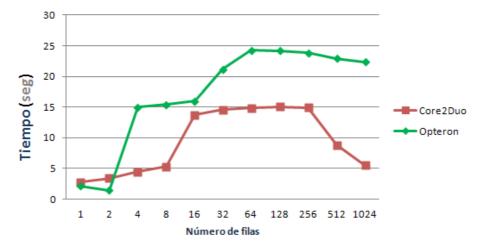

| Figura 31: Caso en el que dos filas puedan solapar en un mismo bloque                                |    |

| Figura 32: Salida del simulador de escritura con stride                                              | 59 |

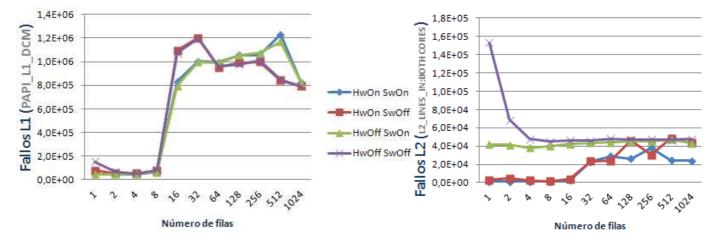

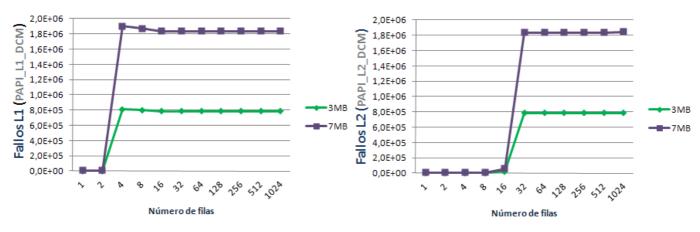

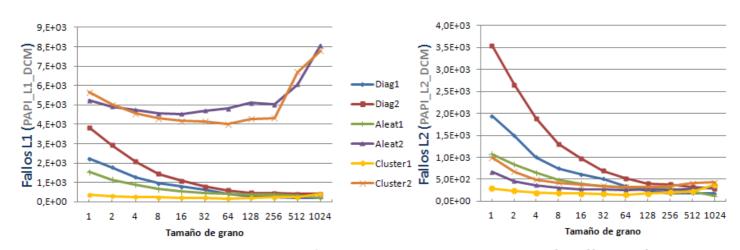

| Figuras 33 y 34: Fallos L1 y L2 para experimentos 1 y 2 [ES][Core2Duo]                               |    |

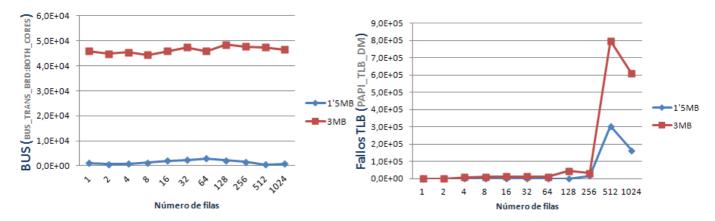

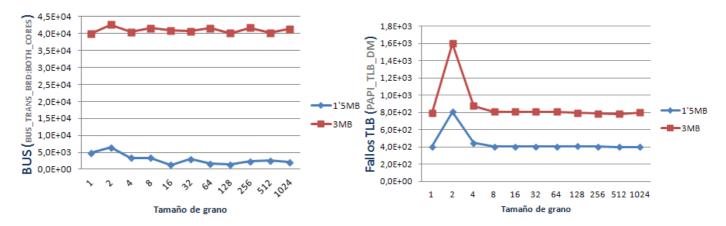

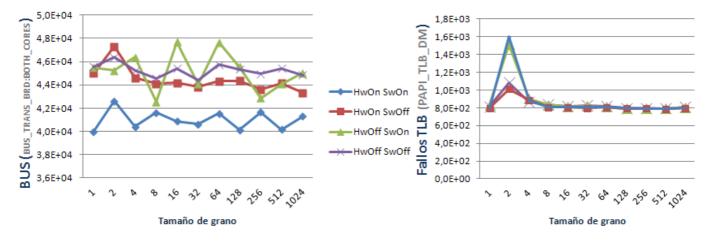

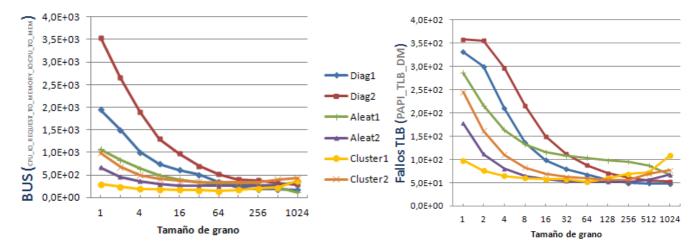

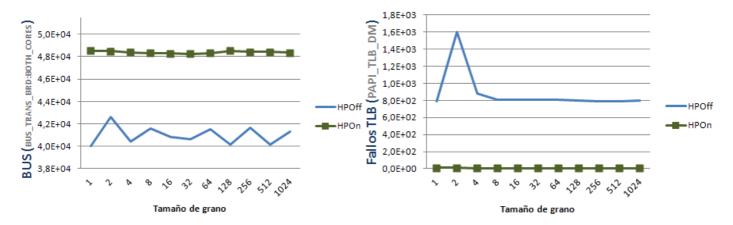

| Figuras 35 y 36: Transferencias de bus y fallos TLB para experimentos 1 y 2 [ES][Core2Duo]           | 60 |

| Figura 37: Muestra de utilización en una iteración                                                   |    |

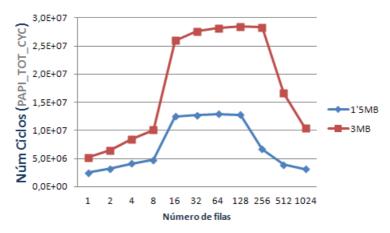

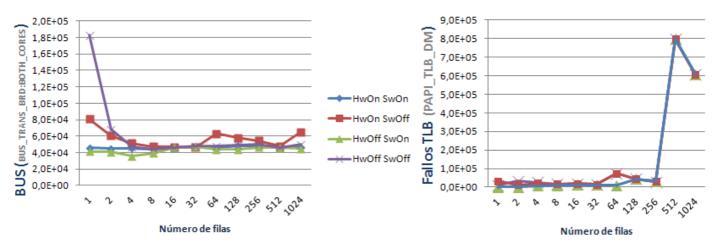

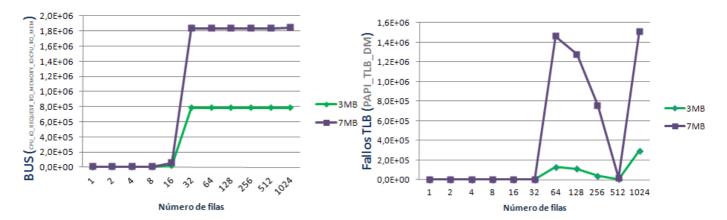

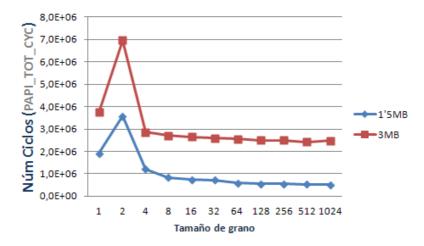

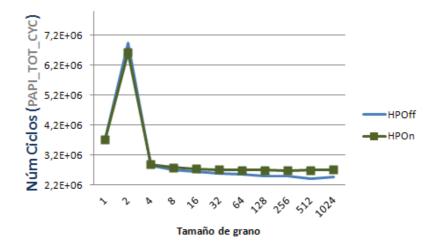

| Figura 38: Número de ciclos para experimentos 1 y 2 [ES][Core2Duo]                                   |    |

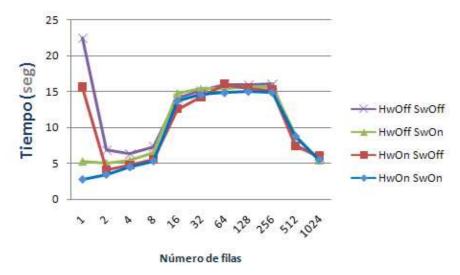

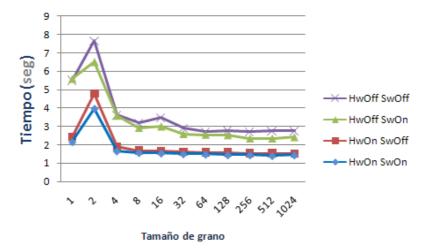

| Figura 39: Tiempo registrado para experimentos 2, 3, 4 y 5 [ES][Core2Duo]                            |    |

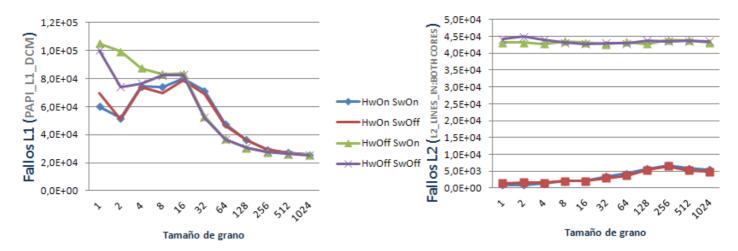

| Figuras 40 y 41: Fallos L1 y L2 para los experimentos 2, 3, 4 y 5 [ES][Core2Duo]                     |    |

| Figuras 42 y 43: Transferencias de bus y fallos TLB para experimentos 2, 3, 4 y 5 [ES][Core2Duo]     |    |

| Figura 44: Número de ciclos para experimentos 2, 3, 4 y 5 [ES][Core2Duo]                             |    |

| Figura 45: Tiempos para experimentos 6 y 7 [ES][Opteron]                                             |    |

| Figuras 46 y 47: Fallos L1 y L2 para los experimentos 6 y 7 [ES][Opteron]                            |    |

| Figuras 48 y 49: Transferencias de bus y fallos TLB para experimentos 6 y 7 [ES][Opteron]            |    |

| Figura 50: Número de ciclos para experimentos 6 y 7 [ES][Opteron]                                    |    |

| Figura 51: Tiempos para experimentos 2 y 6 [ES][Core2Duo y Opteron]                                  |    |

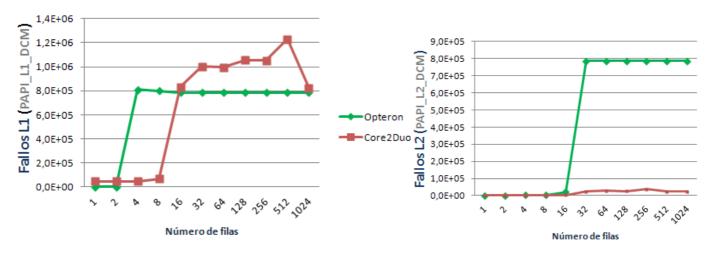

| Figuras 52 y 53: Fallos L1 y L2 para los experimentos 2 y 6 [ES][Core2Duo y Opteron]                 |    |

| Figuras 54 y 55: Fallos TLB y número de ciclos para experimentos 2 y 6 [ES][Core2Duo y Opteron]      |    |

| Figura 56: Tiempos para experimentos 8 y 9 [FS][Core2Duo]                                            |    |

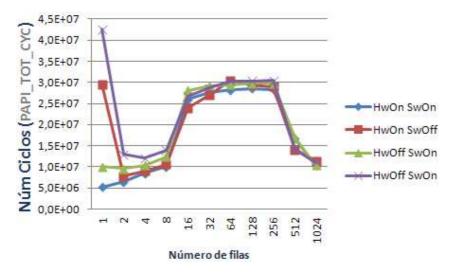

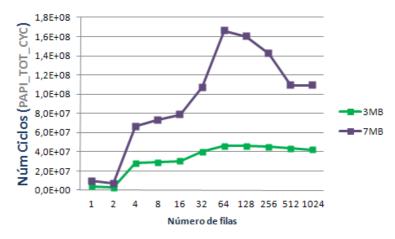

| Figuras 57 y 58: Fallos L1 y L2 para experimentos 8 y 9 [FS][Core2Duo]                               |    |

| Figuras 59 y 60: Transferencias de y fallos TLB para experimentos 8 y 9 [FS][Core2Duo]               |    |

| Figura 61: Número de ciclos para experimentos 8 y 9 [FS][Core2Duo]                                   |    |

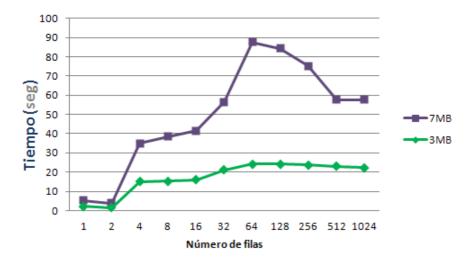

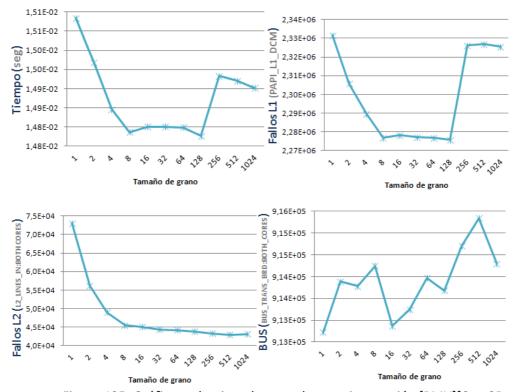

| Figura 62: Tiempo registrado para experimentos 9, 10, 11 y 12 [FS][Core2Duo]                         |    |

| Figuras 63 y 64: Fallos L1 y L2 para experimentos 9, 10, 11 y 12 [FS][Core2Duo]                      |    |

| Figuras 65 y 66: Transferencias de bus y fallos TLB para experimentos 9, 10, 11 y 12 [FS][Core2Duo]                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

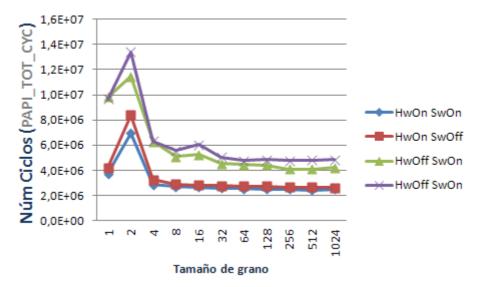

| Figura 67: Número de ciclos para experimentos 9, 10, 11 y 12 [FS][Core2Duo]                                                                                                                        |     |

| Figura 68: Tiempo registrado para experimentos 13 y 14 [FS][Opteron]                                                                                                                               |     |

| Figuras 69 y 70: Fallos L1 y L2 para experimentos 13 y 14 [FS][Opteron]                                                                                                                            |     |

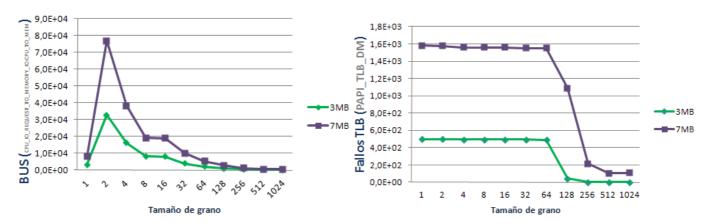

| Figuras 71 y 72: Peticiones al bus de memoria y fallos TLB para experimentos 13 y 14 [FS][Opteron]                                                                                                 |     |

| Figura 73: Número de ciclos para experimentos 13 y 14 [FS][Opteron]                                                                                                                                |     |

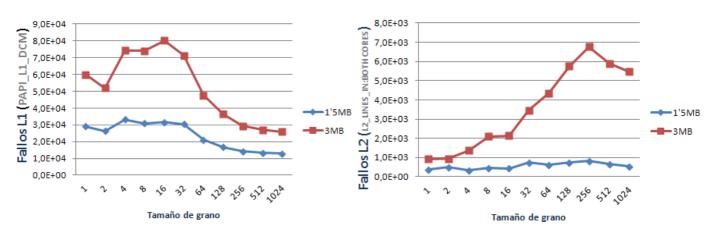

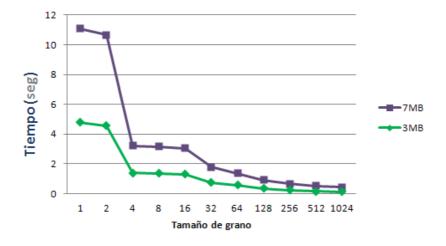

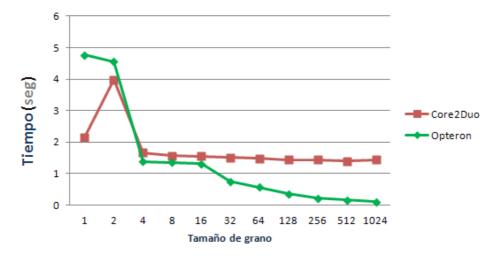

| Figura 74: Tiempo registrado para experimentos 9 y 13 [FS][Core2Duo y Opteron]                                                                                                                     | 76  |

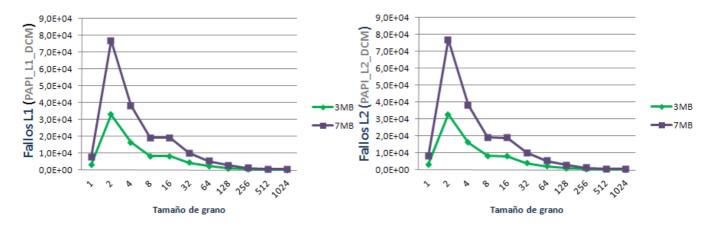

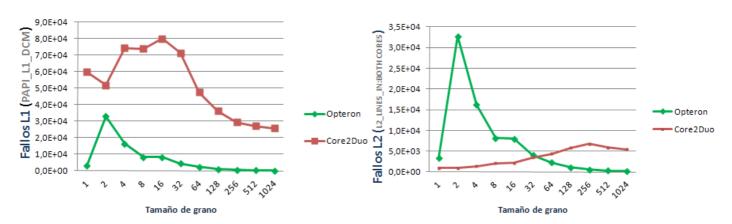

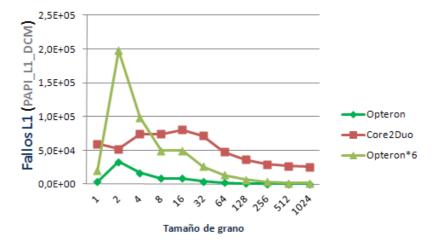

| Figuras 75 y 76: Fallos L1 y L2 para experimentos 9 y 13 [FS][Core2Duo y Opteron]                                                                                                                  | 76  |

| Figura 77: Explicación comparativa fallos L1 en false sharing [FS][Core2Duo y Opteron]                                                                                                             | 77  |

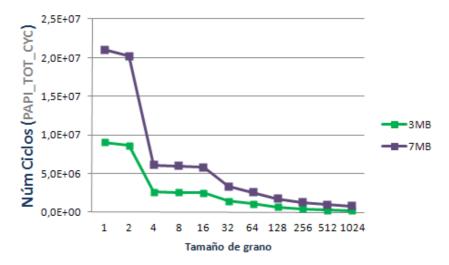

| Figuras 78 y 79: Fallos TLB y número de ciclos para experimentos 9 y 13 [FS][Core2Duo y Opteron]                                                                                                   | 77  |

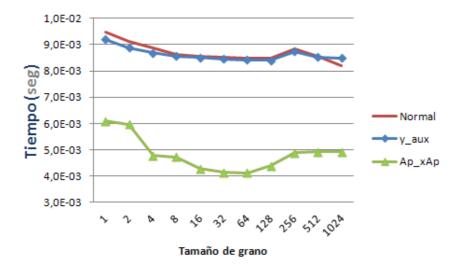

| Figura 80: Tiempos para el experimento 15' [PMV][Opteron]                                                                                                                                          | 79  |

| Figura 81: Accesos iteración a matriz concentrada y dispersa                                                                                                                                       | 80  |

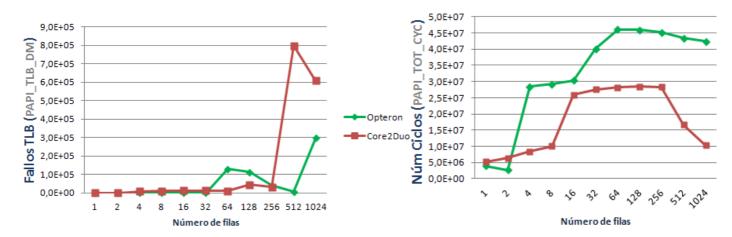

| Figuras 82 y 83: Tiempos para el experimento 15 con/sin dispersión 1 [PMV][Core2Duo]                                                                                                               | 81  |

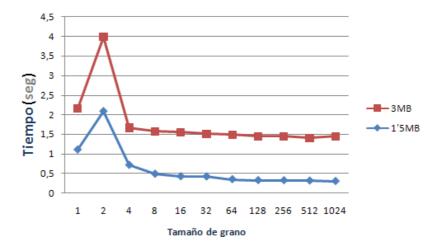

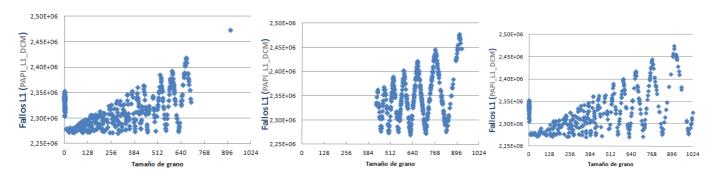

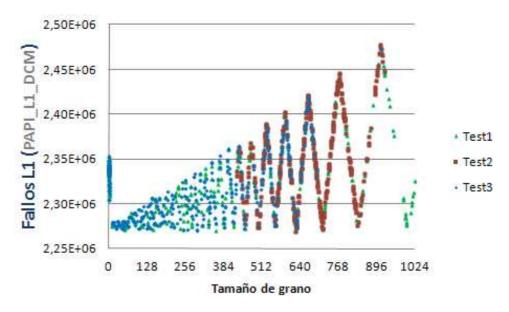

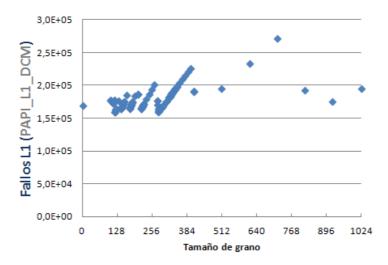

| Figuras 84 y 85: Fallos L1 para el experimento 15 con/sin dispersión 1 [PMV][Core2Duo]                                                                                                             | 82  |

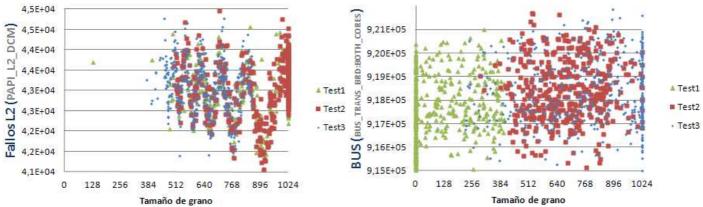

| Figuras 86 y 87: Fallos en L2 y transferencias de bus para el experimento 15 [PMV][Core2Duo]                                                                                                       | 82  |

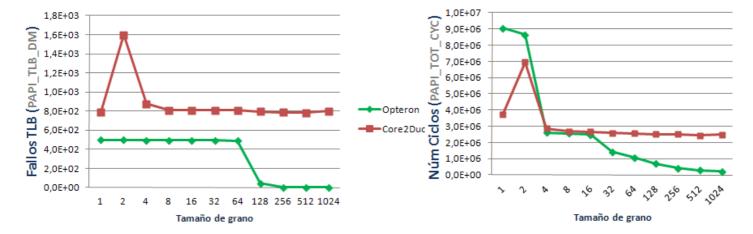

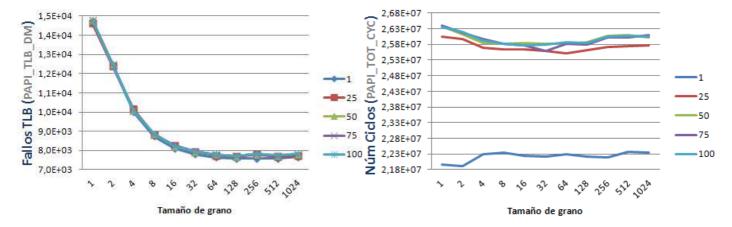

| Figuras 88 y 89: Fallos en TLB y número de ciclos para el experimento 15 [PMV][Core2Duo]                                                                                                           | 83  |

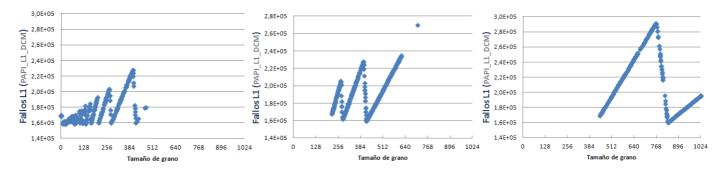

| Figura 90: Tiempo para el experimentos 16 [PMV][Opteron]                                                                                                                                           |     |

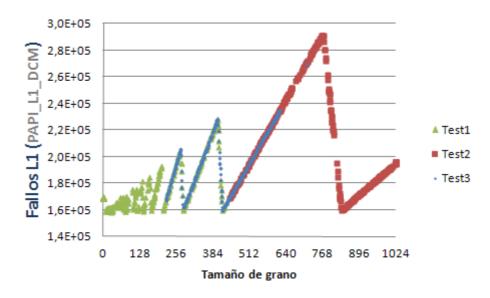

| Figuras 91 y 92: Fallos en L1 y L2 para el experimento 16 [PMV][Opteron]                                                                                                                           |     |

| Figuras 93 y 94: Peticiones al bus de memoria y fallos TLB para el experimento 16 [PMV][Opteron]                                                                                                   |     |

| Figura 95: Tiempos para los experimentos 15 y 16 [PMV][Core2Duo yOpteron]                                                                                                                          |     |

| Figuras 96 y 97: Fallos en L1 y L2 para los experimentos 15 y 16 [PMV][Core2Duo yOpteron]                                                                                                          |     |

| Figuras 98 y 99: Fallos en TLB y número de ciclos para los experimentos 15 y 16 [PMV][Core2Duo y                                                                                                   |     |

| Opteron]                                                                                                                                                                                           | 87  |

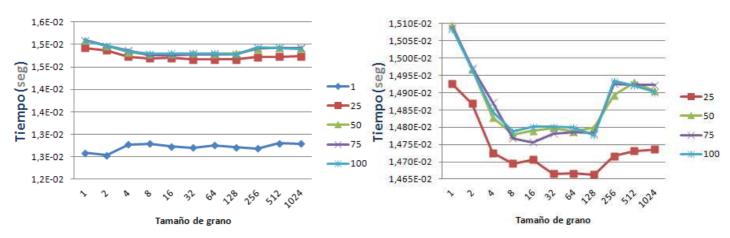

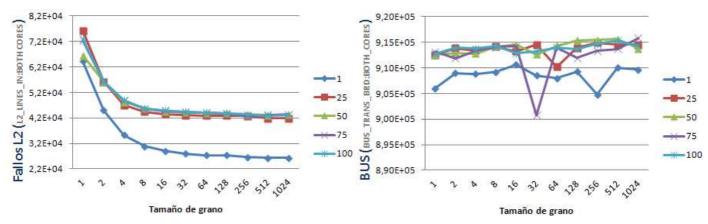

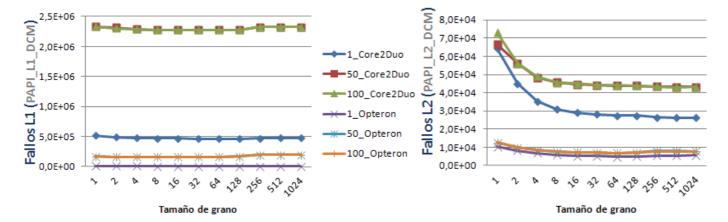

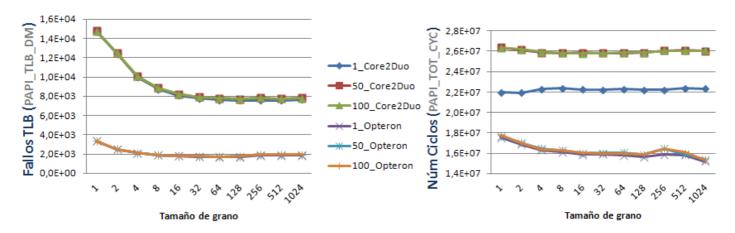

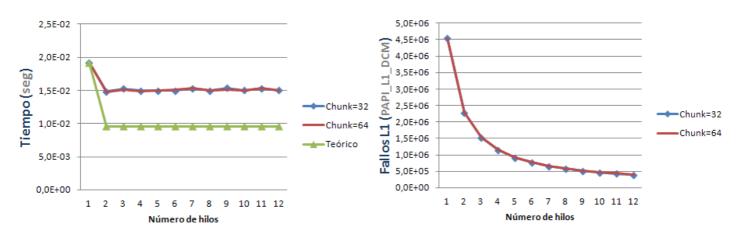

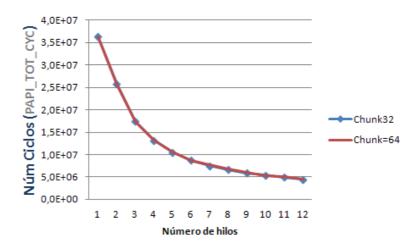

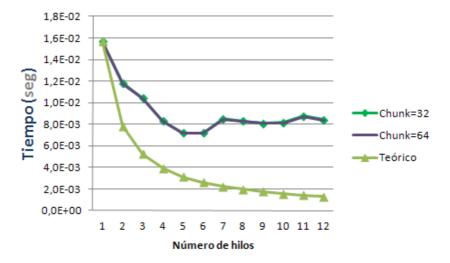

| Figuras 100 y 101: Tiempos y fallos en L1 para el experimento 17 [PMV][Core2Duo]                                                                                                                   |     |

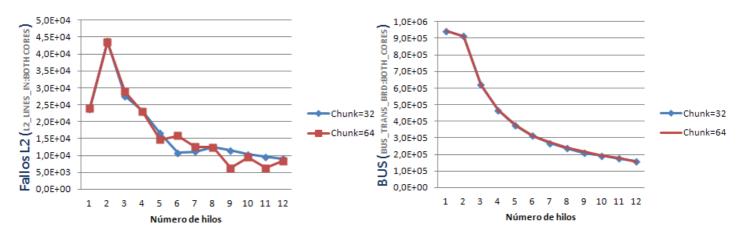

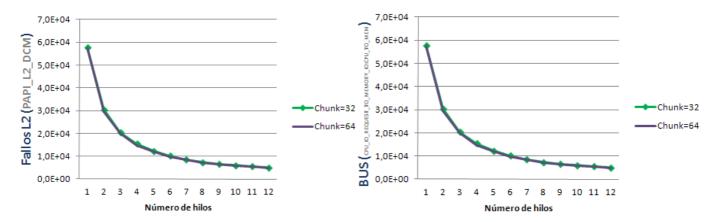

| Figuras 102 y 103: Fallos en L2 y transferencias de bus para el experimento 17 [PMV][Core2Duo]                                                                                                     |     |

| Figuras 104: Número de ciclos para el experimento 17 [PMV][Core2Duo]                                                                                                                               |     |

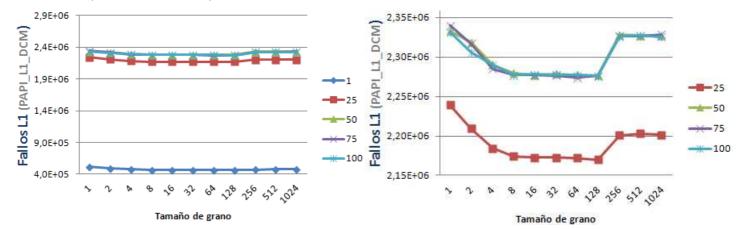

| Figura 105: Tiempos para el experimento 18 [PMV][Opteron]                                                                                                                                          |     |

| Figuras 106 y 107: Fallos en L2 y transferencias de bus para el experimento 18 [PMV][Opteron]                                                                                                      |     |

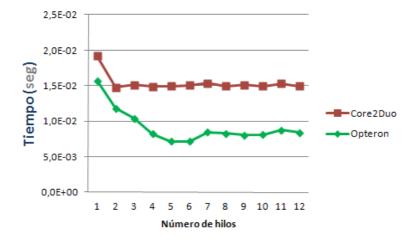

| Figura 108: Tiempos para experimentos 17 y 18 [PMV][Core2Duo y Opteron]                                                                                                                            |     |

| Figuras 109 y 110: Tiempos para el experimento 19 con/sin Diag2 [PMV][Opteron]                                                                                                                     |     |

| Figuras 111 y 112: Fallos en L1  y transferencias de bus para el experimento 19 [PMV][Opteron]                                                                                                     |     |

| Figuras 111 y 112. Fanos en E1-y transferencias de bas para el experimento 19 [PMV][Opteron]<br>Figuras 113 y 114: Peticiones el bus de memoria y fallos TLB para el experimento 19 [PMV][Opteron] |     |

| Figura 115 : Explicación a los fallos en TLB par tamaño de grano fino 19 [Fiviv][Opteron]                                                                                                          |     |

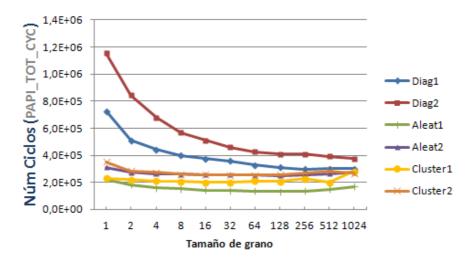

| Figura 116: Número de ciclos para el experimento 19 [PMV][Opteron]                                                                                                                                 |     |

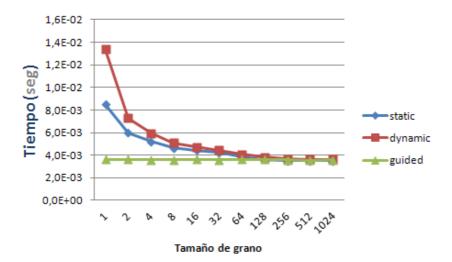

| Figura 117: Tiempo en segundos para el experimento 19 [PMV][Opteron]                                                                                                                               |     |

|                                                                                                                                                                                                    |     |

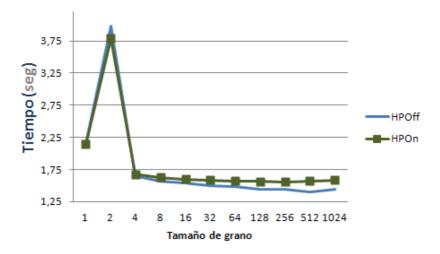

| Figura 118: Tiempo en segundos para los experimentos 9 y 21 [FS][Core2Duo]                                                                                                                         |     |

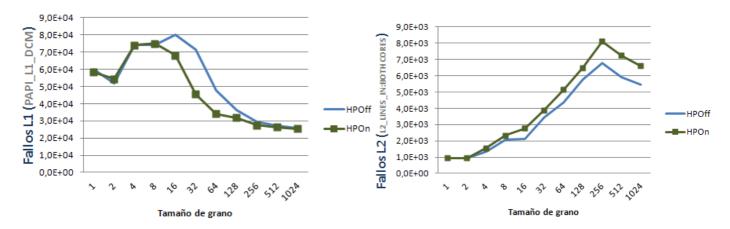

| Figuras 119 y 120: Fallos en L1 y L2 para los experimentos 9 y 21 [FS][Core2Duo]                                                                                                                   |     |

| Figuras 121 y 122: Transferencias de bus y fallos en TLB para los experimentos 9 y 21 [FS][Core2Duo]                                                                                               |     |

| Figura 123: Número de ciclos para los experimentos 9 y 21 [FS][Core2Duo]                                                                                                                           |     |

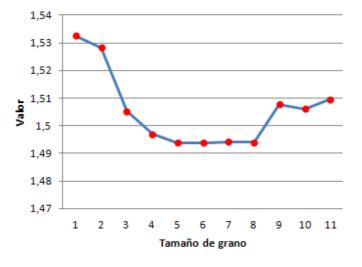

| Figura 124: Función creada a partir de 11 puntos                                                                                                                                                   |     |

| Figura 125: Gráficas seleccionadas para la experimentación [PMV][Core2Duo]                                                                                                                         |     |

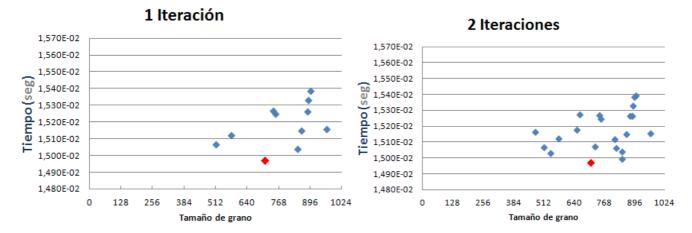

| Figuras 126 y 127: Puntos testeados por Simulated Annealing, 1 y 2 iteraciones [PMV][Core2Duo]1                                                                                                    |     |

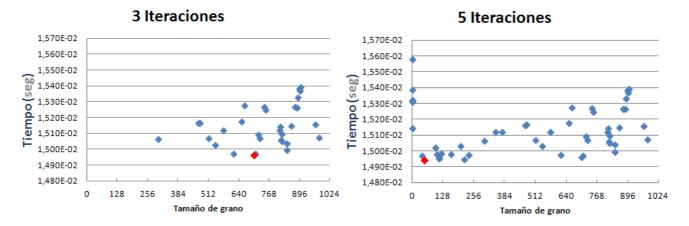

| Figuras 128 y 129: Puntos testeados por Simulated Annealing, 3 y 5 iteraciones [PMV] [Core2Duo]1                                                                                                   |     |

| Figuras 130 y 131: Puntos testeados por Simulated Annealing, 25 y 45 iteraciones [PMV][Core2Duo] .1                                                                                                |     |

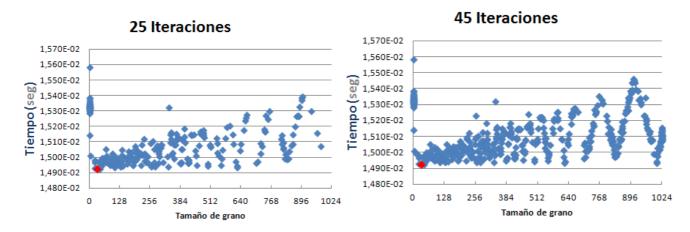

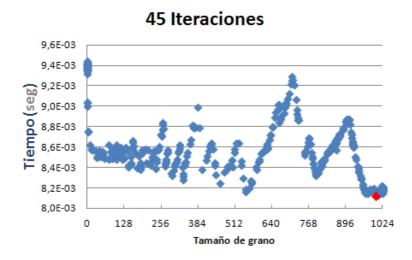

| Figuras 132 y 133: Puntos testeados por Simulated Anneling, 45 Iteraciones [PMV][Opteron]1                                                                                                         |     |

| Figuras 134, 135 y 136: Gráficas generadas por Simulated Annealing con distintas configuraciones para                                                                                              |     |

| fallos en L1 después de 45 Iteraciones [PMV][Core2Duo]1                                                                                                                                            |     |

| Figuras 137, 138 y 139: Gráficas generadas por Simulated Annealing con distintas configuraciones para                                                                                              | а   |

| fallos en L1 después de 45 Iteraciones [PMV][Opteron]1                                                                                                                                             |     |

| Figura 140: Muestra de los tres test en la misma gráfica [PMV][Core2Duo]1                                                                                                                          | .04 |

| Figura 141: Muestra de los tres test en la misma gráfica [PMV][Opteron]1                                                                                                                           |     |

| Figuras 142 y 143: Fallos en L2 y transferencias de bus con Simulated Annealing (3 tests) [PMV][Optero                                                                                             | n]  |

| 1                                                                                                                                                                                                  | .05 |

| Figuras 144 y 145: Fallos en L2 y transferencias de bus con Simulated Annealing (3 tests)                                                                                                          |     |

| [PMV][Core2Duo]                                                                                                                                                                                    | .06 |

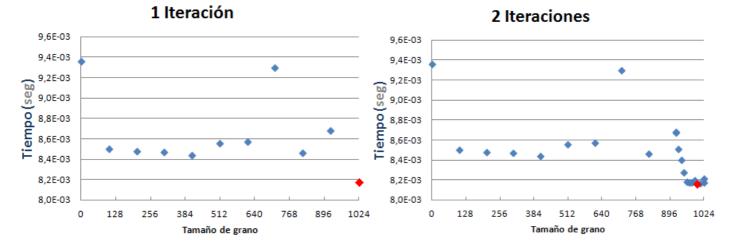

| Figuras 146 y 147: Puntos testeados por la Búsqueda N-aria, 1 y 2 iteraciones [PMV][Opteron]1                                                                                                      | .07 |

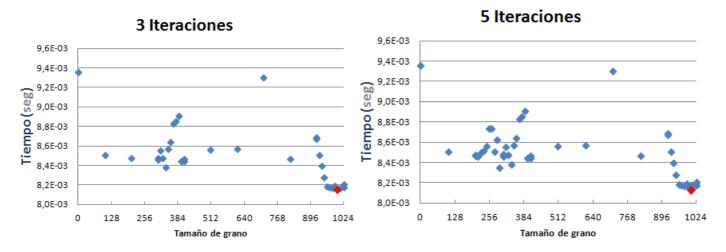

| Figuras 148 y 149: Puntos testeados por la Búsqueda N-aria, 3 y 5 iteraciones [PMV][Opteron]1                                                                                                      |     |

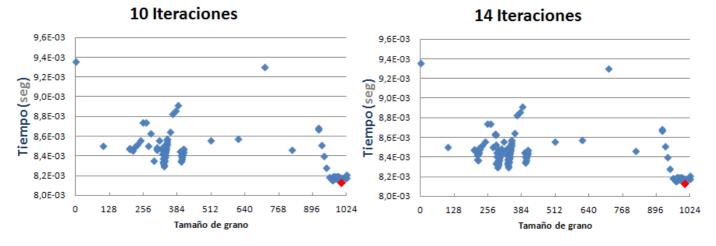

| Figuras 150 y 151: Puntos testeados por la Búsqueda N-aria, 10 y 14 iteraciones [PMV][Opteron]1                                                                                                    |     |

| Figura 152: Fallos en L1 generados por la Búsqueda N-aria [PMV][Opteron]                         |     |

|--------------------------------------------------------------------------------------------------|-----|

| Figura 153: Fases del desarrollo del proyecto junto con las tutorías                             |     |

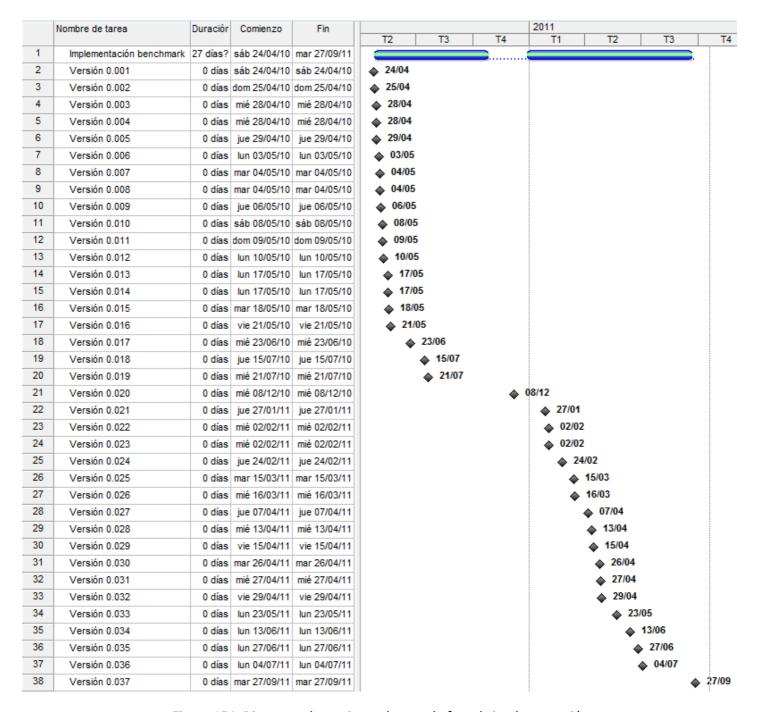

| Figura 154: Diagrama de versiones durante la fase de implementación                              |     |

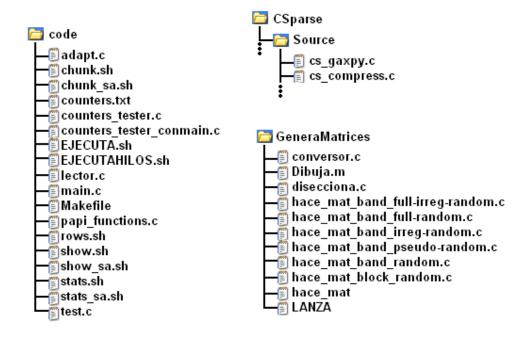

| Figura 155: Diagrama de código generado<br>Figura 156: TaqCloud realizado sobre la memoria       |     |

| Figura 157: Captura de pantalla de la aplicación Perfometer                                      |     |

| ÍNDICE DE TABLAS                                                                                 |     |

| Tabla 1: Especificaciones técnicas de Intel Core de 2 Duo.                                       | 17  |

| Tabla 2: Especificaciones técnicas de AMD Opteron                                                | 20  |

| Tabla 3: Pruebas a lanzar con distintas configuraciones de prefetching                           | 27  |

| Tabla 4: Resumen de experimentos.                                                                | 55  |

| Tabla 5: Resumen de apartados.                                                                   | 56  |

| Tabla 6: Número de filas para llenar caché del Core2Duo.                                         | 60  |

| Tabla 7: Comparativa de características entre Core2Duo y Opteron                                 | 66  |

| Tabla 8: Cálculo de tamaño de vectores en producto matriz-vector.                                | 81  |

| Tabla 9: Diferencias de fallos L1 y L2, entre Core2Duo y Opteron                                 | 86  |

| Tabla 10: Matrices a utilizar para la comparativa.                                               | 92  |

| Tabla 11: Iteraciones asignadas por hilo con planificación guided                                | 97  |

| Tabla 12: Iteraciones asignadas por hilo con planificación static ó dynamic                      | 97  |

| Tabla 13: Resultados de Simulated Annealing y Búsqueda N-aria                                    | 110 |

| Tabla 14: Comparativa de tiempos escritura con stride entre Core2Duo y Opteron                   | 112 |

| Tabla 15: Comparativa de tiempos false sharing entre Core2Duo y Opteron                          | 113 |

| Tabla 16: Comparativa de tiempos producto matriz vector entre Core2Duo y Opteron                 | 114 |

| Tabla 17: Comparativa de tiempos en false sharing con/sin Huge Pages [Core2Duo]                  | 115 |

| ÍNDICE DE CÓDIGO Y SALIDAS                                                                       |     |

| Código 1: Escritura con stride                                                                   | 35  |

| Código 2: False sharing                                                                          | 38  |

| Código 3: Salida del testeador de contadores                                                     | 51  |

| Código 4: Salida de prueba simple                                                                | 52  |

| Código 5: Salida benchmark modo rows, prueba matriz normal                                       | 53  |

| Código 6: Salida final benchmark, prueba producto matriz-dispersa vector                         |     |

| Código 7: Producto matriz-dispersa vector, versión creada por nosotros para que se realice filas |     |

| Código 8: Producto matriz-dispersa vector, sin utilizar compartición de vector escritura         | 78  |

| Código 9: Producto matriz-dispersa vector, sin utilizar la matriz dispersa (se usa un vector)    | 79  |

# 1.- Introducción

En este apartado introductorio trataremos de mostrar escuetamente el mundo de los benchmarks, así como el propósito de este proyecto. En el último apartado se puede ver de forma más concreta, las partes de las que está compuesta la memoria.

## 1.1 Motivación general

El benchmarking es un concepto que se utiliza mucho en la administración de empresas, y que consiste en un proceso encargado de comparar productos o servicios entre distintas compañías, o dentro incluso de una misma corporación <sup>[1]</sup>. El término proviene del inglés y podría traducirse como medida de calidad o punto de referencia <sup>[2]</sup>.

Aplicado a la informática este proceso sirve para comparar el funcionamiento de dos productos, ya sean CPUs, tarjetas de memoria (RAM), tarjetas gráficas, discos duros o cualquier tipo de componente asociado a ellos [3]. Sin embargo, los principales benchmarks tratan únicamente el estudio del rendimiento del procesador. En nuestro caso seguiremos los mismos pasos y abordaremos la parte que concierne a los procesadores. Dentro de los procesadores realizaremos un estudio del funcionamiento dentro de sus memorias internas o cachés, buses y demás factores relacionados con la arquitectura de dichos procesadores.

Actualmente existen benchmarks de distintos tipos, tanto de código abierto (Linkpack [4], NAS Pararell Benchmarks [5]), como de pago (SPEC [6], Futuremark (3DMark) [7]). Los benchmarks se caracterizan por obligar al procesador a realizar un gran número de operaciones. Como se puede observar en la Figura 1, incluso un simple programa capaz de renderizar imágenes puede ser utilizado como benchmark. Esto se debe a que renderizar este tipo de imágenes puede llevar horas y horas de ejecución.

Figura 1: Imagen renderizada con 3DMark

Existen empresas que están dedicadas totalmente al desarrollo de este tipo de software. Los benchmarks siempre han generado tensiones en el mercado de los superordenadores, ya que son capaces de evaluar al más mínimo detalle, el comportamiento de cualquier tipo de computador actual. Es por ello que se va a implementar un software que intente ser neutral y que no aproveche las características de ninguna arquitectura en específico. Este tipo de neutralidad es difícil de alcanzar. A lo largo de la historia se han realizado benchmarks específicos para ordenadores, como por ejemplo el ICOMP [8], creado por Intel para su línea de procesadores; y viceversa, ordenadores que se crean para pasar ciertos benchmarks con la mayor holgura posible.

La motivación general de este proyecto es la de crear un benchmark adaptativo y universal. Esto quiere decir que será capaz de adaptarse a la plataforma en la que se está ejecutando, de tal forma que, se consiga un mayor beneficio ejecutando este benchmark, con configuraciones que sean más óptimas o eficientes para dicha plataforma.

Además con benchmark universal queremos decir que este software se podrá ejecutar en cualquier tipo de máquina. Aunque es cierto que tendrá que tener un cierto software preinstalado, que se comentará en el Apartado 2.4.

A pesar de la complejidad de crear un benchmark, pretendemos que este código sea lo más transparente posible, y durante la siguiente memoria trataremos de explicar de forma clara y concisa los pasos que sigue el benchmark hasta alcanzar los resultados. Pretendemos por tanto, que la reutilización del todo o de ciertas partes del programa sea una tarea sencilla, así como que sea factible realizar ampliaciones y mejoras sobre la base del desarrollo.

## 1.2 Objetivos del proyecto

Uno de los principales objetivos de este proyecto es tener construido un benchmark capaz de ejecutar distintos tipos de funciones para evaluar el comportamiento del procesador. Además dentro de las distintas funciones pretendemos experimentar con distintos valores, como por ejemplo: el número de núcleos en los que se está ejecutando, o lanzar las tareas realizando distintos tipos de reparto de carga computacional, para los distintos núcleos que posea el procesador.

También se pretende ejecutar en al menos dos computadores distintos, de tal manera que se puedan evaluar los distintos resultados. Y realizar una comparativa sobre las distintas variables que procedamos a medir, en las respectivas máquinas. Siempre teniendo en cuenta que las variables a medir sean las mismas en ambos ordenadores. La comparativa se realizará mediante gráficas. Trataremos de analizar todos los resultados intentando acercarnos de la forma más precisa posible a lo que realmente está sucediendo la CPU.

Las pretensiones a la hora de implementar son las de utilizar software específico que sea utilizado de forma extendida, para que de esta manera podamos centrarnos directamente en el benchmark. Así no tendremos que perder el tiempo en leer y descifrar librerías, para luego tener que modificarlas. Gracias a los avances que se han producido en torno a los benchmarks, y a la creación de código abierto que soporta este tipo de aplicaciones, existen un gran número de herramientas que nos facilitarán la labor. En cuanto a este tipo de herramientas algunas de ellas han sido testeadas a lo largo de su historia y muchas de ellas se utilizan en universidades y centros de investigación. También tendremos en cuenta el soporte que puedan dar los creadores de ciertas herramientas, ya que, es probable que tomemos código y librerías de alguno de ellos, que quizás queramos modificar, para que el comportamiento se aproxime más a la idea de benchmark final que queremos realizar.

El desarrollo del proyecto se realizará en lenguaje C. Esto se debe a que la mayor parte de las librerías de ayuda que vamos a encontrar están en este lenguaje. Por otra parte, también es cierto que otro lenguaje bastante extendido en la creación de benchmarks es Fortran <sup>[9]</sup>. Éste siempre ha estado ligado a la computación de alto rendimiento. Sin embargo, algunas librerías específicas sobre funciones matemáticas no están disponibles en Fortran y es por ello que nos decantamos totalmente por C.

En la parte final del proyecto se pretenderá utilizar algún tipo de herramienta por la cual podamos conocer cuál es el entorno más beneficioso para el ordenador. En otras palabras, intentaremos conocer dentro de las distintas pruebas posibles, cuál es la configuración más óptima para la máquina. Para ello nos centraremos en alguna de las distintas variables de ejecución que poseerá el benchmark. Principalmente en el reparto de carga para los distintos núcleos dentro del procesador.

#### Por tanto, los objetivos son:

- Desarrollo de un benchmark de bajo nivel para analizar y comparar distintas arquitecturas.

- Extraer información del rendimiento del microprocesador mediante contadores hardware.

- Comparar equipos con rendimientos pico, es decir, ejecutar pruebas en situaciones poco comunes que beneficien a unas arquitecturas sobre otras.

- Evaluar y desarrollar técnicas de optimización para determinar la mejor configuración del benchmark en la que mejor se explota la arquitectura.

- Evaluar las dos plataformas reales con múltiples núcleos: Intel Core2Duo y AMD Opteron.

## 1.3 Introducción de la memoria

La memoria la podemos dividir en 6 partes principales:

- Plataforma de evaluación: en este apartado se tratan las dos arquitecturas en las que será lanzado el benchmark, describiendo las características técnicas de éstos. Se realiza una explicación de qué son los contadores hardware y cómo funcionan. Y hablamos del entorno software que utiliza la aplicación. En este entorno software tratamos los programas para ejecutar el benchmark en varios núcleos, la librería que utilizamos para la toma de datos y otros programas necesarios para la ejecución del benchmark.

- Benchmarks de evaluación: comentamos las diferentes funciones que han sido implementadas para evaluar el procesador. Además mostramos una pequeña aproximación de lo que debería suceder teóricamente antes de la parte de análisis y experimentación. Finalmente tratamos con técnicas de optimización para conseguir una configuración ideal de benchmark para una cierta CPU.

- <u>Experimentos</u>: es la parte donde se muestran los frutos de la implementación, esto es, los resultados de las diferentes funciones para distintas configuraciones. Intentaremos explicar de la forma más aproximada posible lo que realmente está sucediendo y el porqué de las gráficas resultantes.

- <u>Comparativa final</u>: resumiremos los resultados de las funciones para cada arquitectura y daremos una visión general de en qué contextos funciona mejor una arquitectura u otra.

- <u>Presupuesto</u>: donde tratamos de reflejar el coste aproximado del proyecto y la planificación de éste.

- <u>Conclusiones</u>: para finalizar en esta sección explicaremos alguna de las ideas finales del proyecto y de las dificultades y ventajas de adentrase en un proyecto de este tipo.

Como el lector habrá podido comprobar en la parte inicial de la memoria posee un índice general, así como de un índice para las figuras y tablas que aparecen en la documentación.

Además en la parte final existen dos apartados: un apartado referencias, donde podrá comprobar las fuentes que fueron utilizadas durante la redacción de esta memoria y un apartado glosario donde podrá consultar las definiciones de los términos clave.

El documento también está formado por varios apéndices, que tratan de explicar con ejemplos prácticos, las librerías que fueron utilizadas para el desarrollo del benchmark.

Dentro de los apéndices se encuentra el manual de usuario donde comentamos los pasos que hay que seguir, así como las sentencias y parámetros a ejecutar para utilizar el benchmark.

# 2.-Plataforma de evaluación

El software será evaluado en dos plataformas. A primera vista, pueden parecer pocas, sin embargo la gran cantidad de datos que vamos a obtener de cada de una de ellas y el amplio abanico de pruebas que pueden ser realizadas, hacen de esta elección una buena base para poder testear todos los objetivos iniciales del benchmark.

### 2.1 Intel Core 2 Duo T7100

Esta primera arquitectura está montada sobre un ordenador portátil Toshiba Satellite A200-1dy. Este portátil consta de dos placas de memoria RAM DDR2 de 512MB, una capacidad de 120GB, y el procesador es un Intel Core 2 Duo T7100 [10].

En esta máquina se desarrolla el código, aunque a priori sabíamos que la ejecución en el AMD, desencadenaría errores no controlados en el código inicial que implicarían cambios, debido a que son dos arquitecturas distintas.

| La arquitectura del Co | re 2 L | 0uo 17100 es la s | siguiente '': |

|------------------------|--------|-------------------|---------------|

| Característica         | Nº     | Valor             | Tipo          |

| Característica         | Nº | Valor     | Tipo       | Más datos            |

|------------------------|----|-----------|------------|----------------------|

| Número de núcleos      | 2  | 1.800 GHz | -          | -                    |

| Caché L1 Datos         | 2  | 32KB      | Privada    | Asociativa de 8 vías |

| Caché L1 Instrucciones | 2  | 32KB      | Privada    | Asociativa de 8 vías |

| Caché L2               | 1  | 2MB       | Compartida | Asociativa de 8 vías |

| Transferencia de bus   | -  | 800 MHz   | -          | -                    |

Tabla 1: Especificaciones técnicas de Intel Core de 2 Duo.

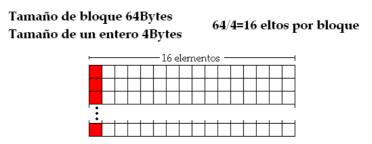

El tamaño de bloque de las memorias es de 64 Bytes, que es el tamaño con el que se van a comunicar entre sí las distintas memorias cachés. La política de reemplazos es LRU, es decir, el bloque de memoria que menos se utilice es que va a ser marcado para que cualquier bloque nuevo pueda ocupar su lugar. Para saber que significa asociativa de 8 vías vamos a explicar resumidamente cómo funciona la memoria internamente.

La memoria caché se encuentra integrada dentro del procesador y su implantación se debe a que es una memoria de rápido acceso. Al requerir un dato de la memoria principal, el procesador mirará antes si este dato se encuentra en alguna de sus memorias cachés. Aunque pueda parecer un paso más en algunos casos, está demostrado que la memorias cachés funcionan de forma eficiente, debido a que los programas suelen utilizar las mismas zonas de memoria (mismos datos) de forma redundante, por lo que los datos almacenados en las memorias cachés, son de crucial importancia a la hora de reducir tiempos de ejecución.

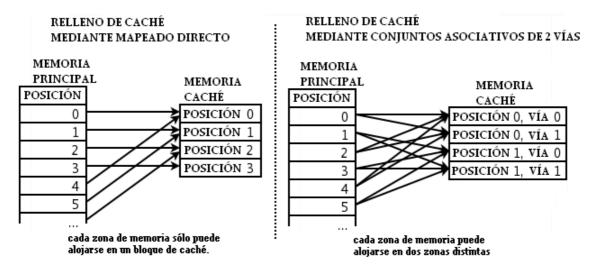

Cuando una zona de memoria no se encuentra precargada en la memoria principal, se produce lo que se conoce como un fallo en la memoria caché. En este caso se procede a cargar este bloque. La decisión de dónde se va a alojar viene dada por la función de correspondencia, si hablásemos de correspondencia directa estaríamos diciendo que cada bloque sólo puede ir alojado en una zona de memoria concreta. Si hablásemos de una función de correspondencia asociativa de 2 vías, como es el caso de la Figura 2, que se muestra a continuación, estaríamos hablando de que cada bloque de memoria puede alojarse en dos zonas de la memoria caché.

Figura 2: Funciones de correspondencia directa y asociativa por conjuntos de 2 vías.

En el caso del Core 2 Duo, cada bloque de memoria puede alojarse en 8 posiciones distintas, lo que puede parecer mucho. Sin embargo, cada bloque de memoria ocupa 64B, y teniendo en cuenta que la L1 de datos ocupa 32KB, estamos hablando de 512 posiciones distintas. La ventaja real está a la hora de buscar, ya que, sólo miraremos en 8 de las 512 posiciones para saber si tenemos un acierto o fallo caché. En el caso de L2 hablamos de más de 32 mil posiciones.

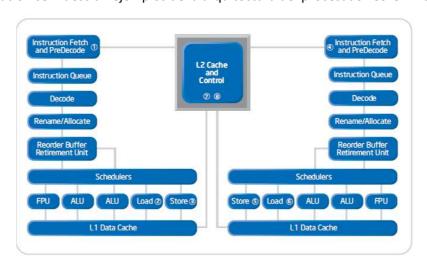

Una de las características a destacar de esta arquitectura es que utiliza la que Intel Ilama "Advanced Smart Caché", que consiste en que la caché de nivel 2 es compartida. Comparada con una caché L2 privada para cada núcleo, la principal ventaja de este método es que ambos núcleos pueden compartir datos sin tener que acceder al bus de memoria. Por lo que reduce los accesos a memoria principal y optimiza el funcionamiento de L2 (desparecen las redundancias).

A continuación se muestran ejemplos de la arquitectura del procesador Core 2 Duo [12].

Figura 3: Arquitectura del procesador Intel Core 2 Duo.

Figura 4: Gráfica de situación de la caché L2 en un Core 2 Duo

Además dentro de esta tecnología también se engloban técnicas de acceso inteligente a la memoria. La idea consiste en trabajar en los dos criterios más conocidos de acceso a memoria. Hablamos de las restricciones temporal y espacial. La <u>restricción temporal</u> dice que zonas de memoria que han sido accedidas recientemente volverán a ser accedidas en un futuro. La <u>restricción espacial</u> dice si una zona de memoria es accedida, es bastante probable que zonas de memoria contiguas sean accedidas.

Core 2 Duo introduce un mecanismo especulativo que predice si una lectura de una instrucción es susceptible de depender de escrituras que están siendo procesadas, de esta forma puede ser procesada sin tener que esperar a la finalización de las escrituras. Este rol predictivo acaba con las ambigüedades y se llama "Memory Disambiguation". Detrás de esta reducción de la espera, el principal objetivo es reducir la dependencia entre las instrucciones incrementando la eficiencia general del programa [13].

Esta arquitectura también posee *prefetching*. El *prefetching* es una técnica que intenta adivinar o predecir que instrucciones van a ser cargadas posteriormente. De tal forma, que cuando el bus se encuentra libre de trabajo, comienza a cargar en memoria caché, bloques de memoria que supuestamente van a ser utilizados. Sobre esta parte ampliaremos en el Apartado 2.4.3.1 y en la parte de la experimentación donde se habla de la desactivación de esta técnica.

### **2.2 AMD Opteron 6168**

El segundo procesador que vamos a utilizar para la ejecución del benchmark va a ser el AMD Opteron 6168. La cesión de esta máquina para las pruebas fue gracias a la Universidad Carlos III y en concreto agradecemos su ayuda al profesor y doctor Francisco Javier García Blas, por configurar esta plataforma para que pudiese ser utilizada.

Mostramos las características principales [14], al igual que hicimos con el anterior procesador:

| Característica         | Nº | Valor     | Tipo       | Más datos                            |

|------------------------|----|-----------|------------|--------------------------------------|

| Número de núcleos      | 12 | 1.900 MHz | -          | -                                    |

| Caché L1 Datos         | 12 | 64KB      | Privada    | Asociativa de 2 vías <sup>[15]</sup> |

| Caché L1 Instrucciones | 12 | 64KB      | Privada    | Asociativa de 2 vías                 |

| Caché L2               | 12 | 512KB     | Privada    | Asociativa de 16 vías                |

| Caché L3               | 2  | 6MB       | Compartida | Se comparte en grupos de 6           |

| Transferencia de bus   | -  | 3200MHz   | -          | -                                    |

Tabla 2: Especificaciones técnicas de AMD Opteron.

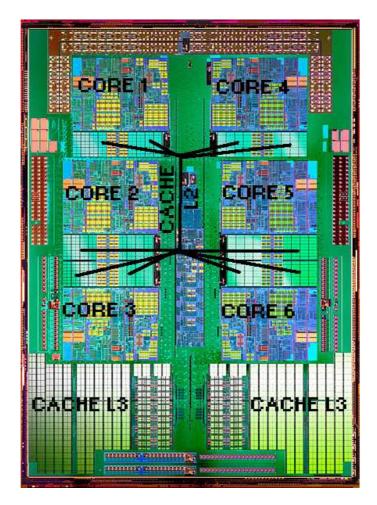

Si comparamos estos datos directamente con los del Core 2 Duo, las diferencias son abismales, así como su arquitectura interna. Para empezar el Opteron va a contar con un nivel más de caché y con 10 núcleos más.

Cada núcleo va a poseer su caché L1 privada de datos y de instrucciones, y una caché privada de nivel 2. En cuanto a la caché de nivel 3 se va a repartir, una para un grupo de seis núcleos y la otra para el otro grupo. De tal forma, que si tienen que compartir datos entre dos procesadores que no comparten L3, este dato deberá viajar por el bus.

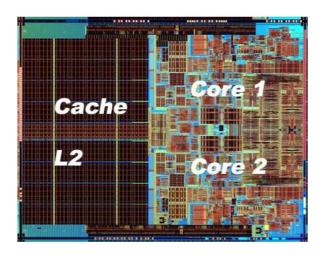

En la Figura 5 veremos la disposición de los núcleos y de las memorias cachés en un AMD Opteron Istanbul con sólo 6 núcleos. Este microprocesador es de la misma familia que el Opteron Magny Course que utilizamos, pero con 6 núcleos menos. Cerca de cada uno de los núcleos tenemos las respectivas cachés de nivel 2 que, como hemos comentado antes son de tipo privado. Abajo del todo tenemos la memoria caché de nivel 3 bien diferenciada, que es compartida, al igual que sucedía en el nivel 2 de la anterior arquitectura descrita.

Dentro de cada uno de los núcleos en amarillo se visualizan las cachés de nivel 1, también diferenciadas en instrucciones y datos. Éstas también son de tipo privado.

Si nos preguntamos qué ventajas tiene que esta máquina posea tantos núcleos, tenemos que verlo desde el punto de vista de los programas que se ven beneficiados de ello. Por ejemplo, en el caso de que necesitemos ejecutar distintas máquinas virtuales vamos a tener un mayor rendimiento, también son buenos sistemas para bases de datos con constantes demandas, ya que puede resolver peticiones de forma paralela y, además, son muy ventajosos para los problemas que nosotros vamos a introducir, y con esto nos referimos al campo de la computación de alto rendimiento, más conocido como high-performance computing (HPC).

Figura 5: Vista ampliada de un Opteron Istanbul

Nuestra tarea va a ser desarrollar un problema que tengan un alto número de operaciones. Estas operaciones deberán ser preferiblemente independientes entre sí de tal forma que la carga se pueda dividir de forma independiente. Cada uno de los núcleos se va a encargar de realizar partes de la carga de trabajo, de tal forma que entre todos contribuyen a solucionar un problema global.

Otra de las ventajas con las que nos encontramos cuando trabajamos en este tipo de procesadores, es que cuentan con distintos canales de memoria. Los distintos canales permiten traer grandes bloques de datos para ser procesados y analizados [16].

Si es cierto, que también tienen algún inconveniente y son los programas mono-hilo, o programas que no pueden ser paralelizados. En ocasiones sucede que algunos programas no pueden ser paralelizados debido al gran número de dependencias entre las operaciones y es por ello que, cuando se ejecutan en este tipo de procesadores, la ganancia no se corresponde de forma directa con el número de núcleos que posea. En estos casos sólo uno de los núcleos se encuentra trabajando mientras que los restantes permanecen ociosos.

### 2.3 Contadores hardware

Los contadores hardware son un conjunto de registros de propósito especial, que se incluyen dentro de los actuales microprocesadores. El objetivo de éstos es el de almacenar estadísticas o eventos que ocurren dentro del procesador. Estos contadores no afectan a la ejecución general del programa ya que, se encuentran implementados como hardware adicional.

En un principio puede parecer que no sean muy necesarios, pero si tenemos cuenta que estamos hablando en un contexto, en el que un supercomputador, como el Blue Gene/P realiza miles de millones de operaciones en un solo segundo y que este segundo de computación puede llegar a suponer un alto coste económico [17]; parece que tiene sentido adentrase en el funcionamiento interno de éstos. Con este tipo de contadores, se intenta extraer el máximo rendimiento de este tipo de sistemas.

Frecuentemente el software se crea específicamente para cada tipo de ordenador en el que va a ser ejecutado. Los equipos de investigación estudian minuciosamente las estadísticas generadas por estos contadores, para medir el rendimiento exacto en sus aplicaciones y para descubrir configuraciones donde pueden conseguir mejoras adicionales.

Como hemos comentado anteriormente, la mayoría de las máquinas actuales se basan en el funcionamiento de carga de datos, mediante memorias cachés. Las memorias cachés ofrecen una mayor velocidad de acceso a los datos y a las instrucciones, de lo que es posible mediante la memoria principal. Por otra parte, la caché se diseña para cumplir los principios de localidad espacial y temporal. Dicho de otra forma, las cachés están diseñadas con la "esperanza" de que una aplicación vuelva a utilizar bloques de memoria que ya utilizó (temporal) y, a que acceda a bloques de memoria cercanos o contiguos a aquellos que ya fueron cargados previamente (espacial). Si una aplicación sigue estos principios, tendremos muchas más opciones de conseguir un alto rendimiento en un procesador cuyo funcionamiento se basa en el uso de memorias cachés. Si no, el rendimiento se desviará de las miras fijadas al comienzo del desarrollo de la aplicación.

El familiarizarse con este tipo de contadores toma algo de tiempo, pero es fácil conocer de forma rápida qué contadores están disponibles en nuestra máquina. Cada procesador tiene un número distinto de contadores, normalmente se nombran de manera distinta. Incluso dentro de diferentes familias o modelos los contadores que se encuentran disponibles pueden diferir enormemente. Sin embargo, como norma general los contadores se encargan de tomar medidas de eventos muy similares.

Dentro de este gran número de contadores podríamos realizar una somera clasificación, intentando agrupar estos en tres conjuntos:

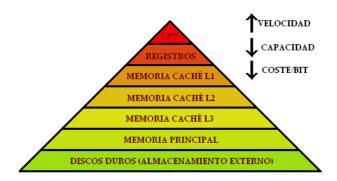

• <u>Caché</u>: Como hemos explicado la mayoría de los sistemas actuales están basados en memorias cachés. El funcionamiento básico de un CPU, es el de intentar operar con datos que se encuentran en sus registros, si no están, deberá acceder a la memoria caché L1 y copiar esta información en sus registros; si esta información no se encuentra en L1, lo que se conoce como un falló caché en L1, deberá acceder a L2, y copiar el dato en L1 y en los registros; y así sucesivamente hasta encontrar

el dato. En el último nivel se encuentra el disco duro, pero esto sale del ámbito del procesador y como máximo estamos limitados al bus de comunicaciones entre la caché de más alto nivel y la memoria principal. A continuación mostramos un gráfico de las memorias (Figura 6), en cuanto a proximidad a la CPU. En algunos sistemas no se cuenta con memoria caché de nivel 3.

Figura 6: Pirámide de tipos de memoria en relación con CPU

Por tanto, vamos a tener datos de estadísticas de <u>accesos</u>, de <u>aciertos</u> (cuando el bloque accedido se encuentre en la memoria), <u>fallos</u> (cuando el bloque accedido no se encuentre en la memoria). La suma de aciertos y fallos es igual al número de accesos (intentos). Además también vamos a poder diferenciar entre los fallos/aciertos que se comentan tanto para <u>instrucciones</u> como para <u>datos</u>. En este caso con instrucción nos referimos a partes del programa que están siendo cargadas para ser ejecutadas y cuando nos referimos a datos, es la información que requiere el programa para seguir ejecutando. Dentro de todo este conjunto también vamos a poder diferenciar las operaciones de <u>lectura</u> y <u>escritura</u> que se realizan en las distintas memorias.

- Instrucciones: Otro tipo de contadores que podemos agrupar es el de las instrucciones. Dentro de un programa pueden generarse un gran número de instrucciones, sin embargo, las que resultan más costosas a un procesador, son las que conllevan operaciones en punto flotante. Estas operaciones implican sumas, multiplicaciones, divisiones y raíces cuadradas, de números de gran tamaño. También existen las denominadas instrucciones SIMD (Single Instruction Multiple Data) que pueden ser contabilizadas para precisión simple o doble. En cuanto a las instrucciones condicionales de salto también pueden ser contabilizadas teniendo en cuenta las veces que se dio o no el salto, y las veces que se predijo correctamente (o no) si se iba a dar el salto. Y en general también se pueden seguir las instrucciones que han sido emitidas y completadas.

- <u>Ciclos:</u> Dentro de esta división estaríamos agrupando los contadores que nos pueden dar información sobre número de ciclos que la máquina está parada, esperando por accesos de memoria, ya sean escrituras o lecturas. O también el número de ciclos que esperamos por cualquier otro recurso, como por ejemplo la unidad de coma flotante. También se puede contabilizar el número total de ciclos que se han llevado a cabo.

Después de esta visión general y clasificada, existen otros tipos de contadores que salen de este grupo y que se pueden mostrar ligados a una arquitectura, esto es, ser específicos de un microprocesador, o aparecer indistintamente en dos microprocesadores con arquitecturas muy dispares. Por ejemplo, el número de fallos en L3 no podrá aparecer en arquitecturas que no dispongan de este nivel de caché. Otro tipo de contadores que pueden aparecer son los relativos al bus, que conecta el microprocesador con la memoria, así como contadores relacionados con *prefetching*.

Los contadores además se clasifican en derivados y no derivados. Un contador derivado es un tipo de contador que se puede calcular a partir de otros contadores. Por ejemplo, el número de accesos (intentos) es igual al número de aciertos más el número de fallos.

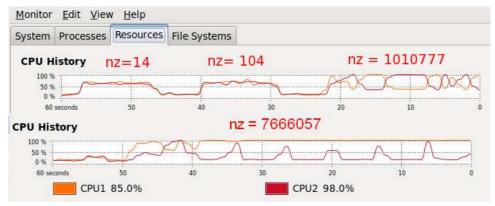

Uno de los grandes problemas de los contadores es que el ordenador tiene un número limitado de registros y, por ello, no puede tomar estadísticas de todos los datos de una sola vez. Es aquí donde entra la multiplexación, mediante ésta se realiza la misma prueba para tomar medidas de distintos contadores. Es importante que la prueba suponga las mismas operaciones y el mismo resultado para el ordenador, puesto que de lo contrario estaríamos tomando medias erróneas. La multiplexación es necesaria a la hora de tomar estadísticas del ordenador, sin embargo supone un aumento importante en el tiempo de ejecución de los benchmarks.

La mejor fuente para conocer los eventos disponibles en nuestro procesador suele aparecer en la referencia técnica de nuestro procesador, frecuentemente disponible en la Web oficial del vendedor.

Otra complicación que podemos encontrar al nivel de *kernel* (núcleo del sistema operativo) es conseguir acceder a estos contadores hardware. Aunque cada vez más se va implantando en los sistemas operativos, e incluso el núcleo del Itanium (IA-64) provee del *driver* oficial (creados por Stephane Eranian [18]), el árbol estándar de versiones Linux para x86 no provee de esta característica.

Afortunadamente, se han realizado esfuerzos sobre estos temas. El primero y uno de los más importantes es el desarrollo de un *driver* de monitorización de estadísticas para el *kernel* x86 denominado *perfctr*. Éste es un parche muy estable desarrollado por Mikael Pettersson de la Universidad Uppsala en Suecia <sup>[19]</sup>. El parche *perfctr* cada vez está siendo más adoptado por la comunidad, y se mantiene y mejora de forma continua. El segundo esfuerzo proviene del Laboratorio de Computación e Innovación de la Universidad de Tennessee-Knoxville, y se denomina PAPI (Performance Application Programming Interface), traducido como Interfaz de Programación de Rendimiento de Aplicaciones. PAPI define un conjunto estándar de eventos que pueden ser monitorizados mediante una librería de sencilla instalación. El proyecto PAPI provee implementaciones para distintos sistemas operativos y para distintos tipos de procesadores. Esto incluye a los procesadores Intel/AMD x86, sistemas Itanium y más recientemente procesadores AMD x86-64. Expandiremos la información sobre PAPI en el Apartado 2.4.2 y en el Apéndice A.

## 2.4 Entorno software

Dentro de este apartado trataremos las distintas librerías y software que han sido utilizados para realizar el benchmark. Cabe destacar que todas ellas son "opensource" o de código abierto, por tanto cualquier puede tener acceso a ellas, así como a sus manuales y soporte online.

#### **2.4.1 OpenMP**

La API de OpenMP nos provee de computación paralela en distintas plataformas, con procesos capaces de compartir memoria <sup>[20]</sup>. Este código lo podemos utilizar tanto para programar en lenguaje C/C++ como para Fortran <sup>[21]</sup>, en todo tipo de arquitecturas, incluyendo plataformas Unix y Windows NT.

Dicho de forma más sencilla, mediante OpenMP vamos a conseguir paralelizar un simple programa, de tal forma que lo que antes se estaba ejecutando por un único proceso ahora se ejecutará en varios hilos. Para ello reparte la carga entre los distintos hilos, para que puedan trabajar conjuntamente y así terminar antes.

Con la paralelización vamos a explotar la ventaja que nos proporcionan los ordenadores con múltiples núcleos. Esto se debe a que cada hilo en el que se separa el programa principal, va a ser ejecutado en un núcleo distinto, y es en este punto donde se consigue realmente la paralelización del programa.

Concretamente, esta API nos va a permitir modificar ciertas variables dentro de cada prueba. Como hemos comentado vamos a poder tratar con distinto número de hilos, pero también vamos a poder experimentar con diferentes tipos de planificación y de reparto de carga. Entre estas variables se encuentran [22]:

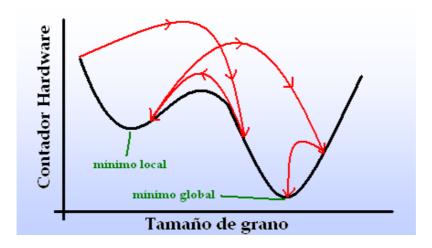

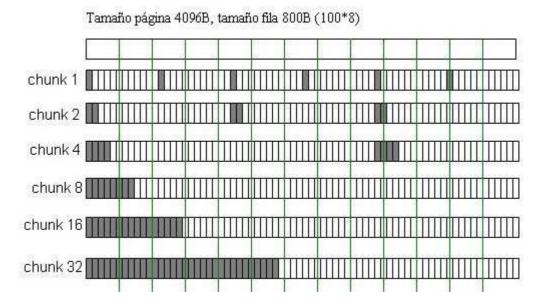

- Chunk: o tamaño de grano, que determinará la carga que se va a asignar para cada hilo. Esta parte es importante, si elegimos mucha cargar a repartir, puede suceder que no haya un buen balance entre procesos y que algunos realicen más trabajo que otros. Si elegimos una carga muy pequeña para cada proceso, tendremos también problemas puesto que no habrá reutilización de zonas de memoria y el prefetching no funcionará tan bien como en otros casos. Además en este último caso es probable que aumente el número de cambios de contexto.

- Nº de hilos o número de subprogramas en los que se dividirá el programa principal. Lo más correcto sería que fuese igual al número de núcleos del ordenador, ya que, si es mayor, habría procesos sin núcleos donde ejecutar. En caso contrario tendríamos núcleos en los que no se está ejecutando ningún hilo.

- Planificación: tipo de reparto que se realizará. OpenMP nos provee de las siguientes opciones: static, dynamic y guided, que veremos con más detalle en el Apartado 4.6.4.

Una de las ventajas más atractivas de esta librería, y quizás la que la ha hecho tan difundida, es que todos estos cambios se pueden incluir añadiendo simplemente dos líneas en

nuestro código original. Mediante ella tomaremos las medidas de tiempos gracias a la función omp\_get\_wtime() y será la única medida separada de tomadas con PAPI.

Como comentamos en el apéndice de PAPI y repetimos aquí, por ser de suma importancia, la toma de tiempos se hará de forma especial para eliminar el propio tiempo de ejecución de la rutina de tiempos. Para ello seguiremos los siguientes pasos: se toman tres medidas de tiempo, una antes del ejecutar el benchmark y dos después

Toma de tiempo T1 Ejecución de Benchmark Toma de tiempo T2 Toma de tiempo T3

Y obtenemos el tiempo real de ejecución con la fórmula:

Ttotal =

$$(T_2 - T_1) - (T_3 - T_2) = 2T_2 - T_1 - T_3$$

#### 2.4.2 Librería PAPI

La librería PAPI será la que nos provea código para acceder a los contadores hardware <sup>[23]</sup> de los que hemos hablado al comienzo del Apartado 2.4. De esta forma vamos a obtener la información de lo que está sucediendo, en cuanto a rendimiento, después de la ejecución del benchmark. En concreto utilizaremos la versión 4.0.0.

El uso de esta librería está bastante extendido y cuenta con varias actualizaciones a sus espaldas, por lo que es una librería bastante robusta. Además posee un manual bastante detallado con ejemplos, que son una guía perfecta para arrancar con la herramienta [24].

Como soporte posee un foro bastante activo, con usuarios que pueden ayudar en caso de dudas, o para resolver algún tema que quede poco claro en el manual [25].

Dentro de la librería PAPI se hace una clara diferencia entre los eventos preestablecidos y los eventos nativos. Los eventos preestablecidos son un conjunto de eventos que se pueden encontrar típicamente en muchas CPUs. Por otra parte, los eventos nativos son eventos propios de una arquitectura en concreto y, por tanto, no pueden ser utilizados en todas las plataformas existentes.

Para utilizar PAPI podemos hacerlo utilizando cualquiera de sus dos interfaces, de alto y bajo nivel. Ambas proveen de funciones para arrancar, parar y leer los contadores de una lista específica de eventos, aunque las diferencias son constatables. Por su parte, la interfaz de alto nivel consigue, de forma más sencilla para el programador, dar acceso a todo tipo de información. Sin embargo, si deseamos tener un mayor control de la aplicación, así como poder acceder indistintamente a eventos preestablecidos como eventos nativos; deberemos hacer uso de la interfaz de bajo nivel. Quizás esta última razón premie sobre todas y ha sido la que nos ha llevado a utilizar la interfaz de bajo nivel de PAPI. Ya que, en nuestro interés está el de usar conjuntamente eventos nativos (específicos de una cierta arquitectura) y eventos preestablecidos.

PAPI también provee de multiplexación. La multiplexación permite leer más contadores de los permitidos por los registros de la plataforma. De esta forma, se le pasa una lista de

contadores y PAPI se encarga de tomar las estadísticas de todos ellos. Uno de los grandes problemas de la multiplexación es que no funciona en todas las plataformas y en concreto en la plataforma en la que vamos a implementar el código, Intel Core2 Duo, no funciona, por lo que en nuestro caso hemos optado por implementar la multiplexación manualmente. Para ello debemos pasar un conjunto limitado de eventos y después realizar las pruebas de nuevo tantas veces como sea necesario hasta que acabemos con el resto de contadores que deseemos monitorizar. Una descripción detallada de los pasos que seguiremos viene en el Apartado 4.1.

La versión que vamos a utilizar de PAPI (4.0.0) no cumple con las normas de Valgrind. Valgrind es un software capaz de detectar fugas de memoria y que es útil para este tipo de software [26], así nos aseguraríamos de que toda la memoria que se utiliza se libera al final de la ejecución, evitando provocar que toda la memoria reservada no sea liberada. Debido a este problema no podremos asegurarnos de que nuestro código no pierda memoria ya que se incrusta junto con las funciones de PAPI y no podemos analizarlo de forma independiente.

En el Apéndice A, se muestra un ejemplo de uso de las librerías de PAPI, en una interfaz de alto y de bajo nivel.

#### 2.4.3 Prefetching

El *prefetching* es una técnica bastante extendida en los microprocesadores actuales. Ésta consiste en cargar bloques de memoria en la memoria caché, ya sean datos o instrucciones, que se supone que van a ser utilizados, ya sea por proximidad o por probabilidad. Las técnicas de *prefetching* intentan predecir de forma más o menos acertada qué zonas de memoria serán utilizadas, para ello realizan un estudio del patrón de acceso a memoria que realiza la CPU en la memoria, y si éste se aleja de la aleatoriedad, el prefetching va a proporcionar muy buenos resultados <sup>[27]</sup>, dado que va a predecir y cargar en la caché los datos que van a ser accedidos en el futuro.

Dentro del *prefetching* se pueden distinguir dos tipos, *prefetching* software y hardware. El *prefetching* software lo realiza el compilador. Éste añade instrucciones de precarga al código original en zonas donde piensa que van a utilizarse datos o instrucciones. Por su parte el *prefetching* hardware funciona totalmente desligado al código y, de forma independiente, carga datos o instrucciones que tienen alta probabilidad de ser utilizados.

La idea es realizar un estudio con las cuatro posibilidades existentes:

| Prefetching   | Hardware | Software |

|---------------|----------|----------|

| Experimento A | 1        | 1        |

| Experimento B | 1        | -        |

| Experimento C | -        | 1        |

| Experimento D | -        | -        |

Tabla 3: Pruebas a lanzar con distintas configuraciones de prefetching

Es decir, activaremos y desactivaremos los distintos tipos de *prefetching* y veremos su comportamiento. Esta idea no es nuestra original y la hemos sacado del siguiente paper de

Intel: Optimizing Embedded System Performance — Impact of Data Prefetching on a Medical Imaging Application [28]. En el que entre otras cosas, se utiliza un generador de imágenes médico (AMIDE [29]). Y como medida se toma el tiempo que tarda el procesador en renderizar una imagen. En la Figura 7 mostramos una captura del AMIDE (A Medical Imaging Data Examiner) software que sirve para analizar y registrar imágenes médicas volumétricas. AMIDE además es un software de licencia libre.

Figura 7: Captura del renderizador de imágenes médicas AMIDE.

#### 2.4.3.1 Prefetching Hardware, MSR-TOOLS

El hardware prefetch no es una nueva técnica. Comenzó a ser utilizada con el Pentium III Tualatin. Sin embargo, fue el Intel Netburst quien lo mejoró fundamentalmente. La gran diferencia entre la frecuencia del procesador y del bus, hizo al Netburst particularmente sensible a los efectos de los fallos cachés, y aumentó fuertemente el interés por un *prefetching* eficiente.

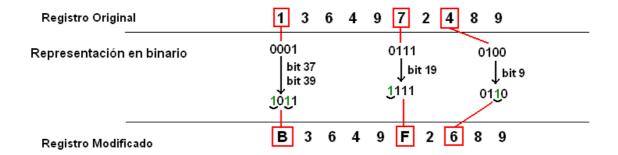

La herramienta MSR-Tools es un software que nos permite acceder a los registros del ordenador, tanto en modo lectura como en modo escritura <sup>[30]</sup>. Uno de los grandes inconvenientes de este software es la falta de manual y de soporte.

Con este software desactivaremos las opciones de *prefetching* del Intel Core2Duo y realizaremos un estudio de lo que está sucediendo.

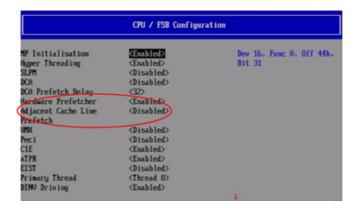

Mediante esta herramienta MSR-TOOLS, vamos a ser capaces de desactivar el *prefetching* hardware. Si bien es cierto que en algunos ordenadores esta opción se puede deshabilitar en la BIOS (véase Figura 8), en nuestro caso no disponemos de esa opción y por eso requerimos de esta herramienta.

Figura 8: Captura en la que la BIOS permite desactivar el prefetching hardware

Para saber que registros vamos a utilizar deberemos consultar la documentación de Intel [31] y de AMD [32], para acceder a los respectivos registros que modifican estas configuraciones.

Uno de los grandes problemas de esta herramienta es que tiene un control de errores muy pobre, ya que podemos introducir cualquier nombre de registro y en la mayoría de los casos no retorna un fallo, diciendo que este registro no existe.

Por ejemplo, si deseamos leer un registro usaremos:

```

registro

tipo salida (hexadecimal)

1364972489 (salida hexadecimal)

```

Y para escribir en el registro de un procesador en concreto:

```

wrmsr -p0 0x1A0 0xB3649F2689 — valor

registro

núcleo (p0,p1...)

```

El caso es que si hacemos un rdmsr del registro "registroinexistente" nos devuelve valores, como si hubiese un registro con ese nombre. Después de probar distintas combinaciones con el registro "MSRC001\_1022 Data Cache Configuration Register (DC\_CFG)" fue imposible modificar los registros en el Opteron. Además cada vez que realizábamos intentos, lanzábamos el benchmark pero las ejecuciones arrojaban los mismos resultados, por lo que no ha sido posible desactivar el hardware *prefetching* del AMD.

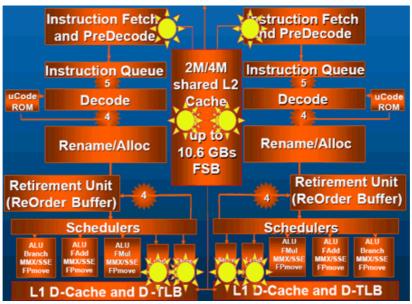

Dentro del Intel Core 2 Duo podemos hablar de distintos mecanismos de *prefetching*:

- El prefetcher de instrucciones precarga instrucciones en la caché de instrucciones L1, basándose en predicciones de salto. Cada uno de los dos cores tiene uno.

- El IP prefetcher (*Instruction Pointer-based prefetcher* o el prefetcher de instrucciones basado en punteros) escrudiña el histórico de lecturas para tener un

diagrama generalizado y cargar "futuros bloques útiles", de datos, en la caché de datos de nivel 1. Cada uno de los dos cores tiene uno.

- El DCU prefetcher (Data Cache Unit Unidad de datos caché) detecta múltiples lecturas de una simple línea de caché durante un determinado tiempo y decide cargar la siguiente línea en la caché L1. También una por cada core

- El DPL prefetcher (Data Prefetch Logic Carga de datos lógica) tiene un comportamiento similar al DCU Prefetcher. La única diferencia es que detecta peticiones en dos líneas consecutivas de caché (N y N+1) y se dispara si la lectura de la línea N+2 mueve el bloque de la memoria a la caché L2. La caché L2 también tiene dos de ellas, pero se comparten dinámicamente entre ambos núcleos.

El número total de prefetchers que hay en el Core2Duo son por tanto los ocho que hemos tratado y se representan mediante soles en la siguiente figura:

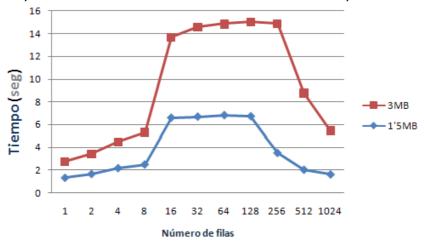

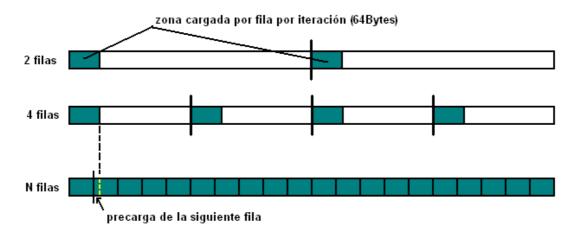

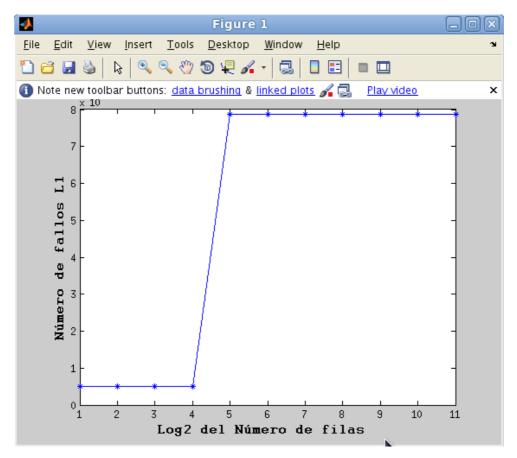

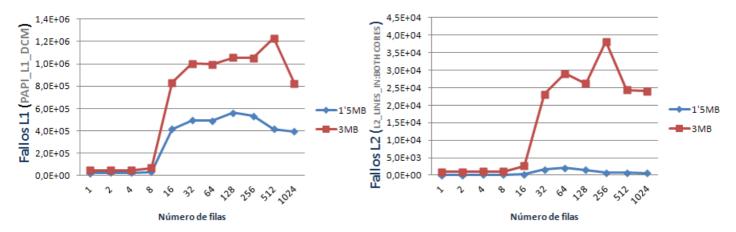

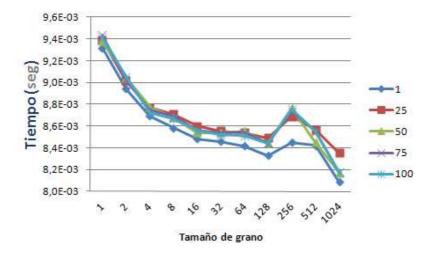

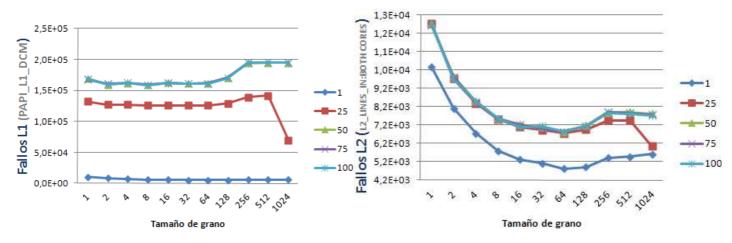

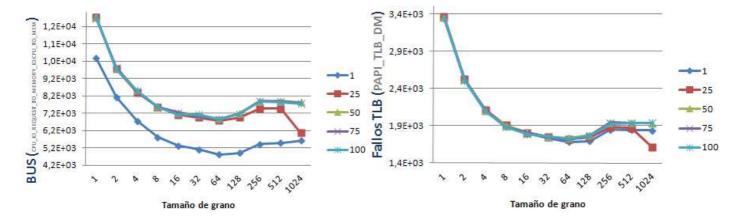

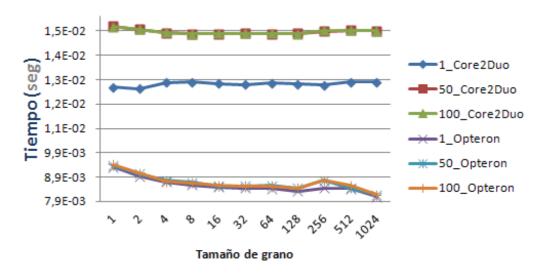

Figura 9: Prefetchers dentro del Intel Core2Duo