### Proceedings of the First PhD Symposium on Sustainable Ultrascale Computing Systems (NESUS PhD 2016) Timisoara, Romania

Jesus Carretero, Javier Garcia Blas Dana Petcu (Editors)

February 8-11, 2016

#### **Volume Editors**

Jesus Carretero University Carlos III Computer Architecture and Technology Area Computer Science Department Avda Universidad 30, 28911, Leganes, Spain E-mail: jesus.carretero@uc3m.es

Javier Garcia Blas University Carlos III Computer Architecture and Technology Area Computer Science Department Avda Universidad 30, 28911, Leganes, Spain E-mail: fjblas@arcos.inf.uc3m.es

Dana Petcu

West University of Timisoara

Department of Computer Science

Faculty of Mathematics & Informatics

B-dul V.Parvan 4, 300223 Timisoara, Romania

E-mail: petcu@info.uvt.ro

#### Published by:

Computer Architecture, Communications, and Systems Group (ARCOS) University Carlos III

Madrid, Spain

http://www.nesus.eu

ISBN: 978-84-608-6309-0

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

This document also is supported by:

Printed in Madrid — February 2016

#### **Preface**

#### **Network for Sustainable Ultrascale Computing (NESUS)**

We are happy to present the Proceedings of the First PhD Symposium on Sustainable Ultrascale Computing Systems (NESUS PhD 2016), an output of the PhD Symposium held in the First Winter School of the COST Action (IC1035) (www.nesus.eu) <a href="http://www.nesus.eu">http://www.nesus.eu</a>)>.

The First PhD Symposium of the COST Action IC1035 was held on February 10, 2016, in Timisoara. Twenty PhD students belonging to NESUS action made a presentation of their PhD Thesis research work and contributed with a short paper reflecting the main ideas of their PhD Thesis.

The PhD Symposium was a very good opportunity for the young researchers to share information and knowledge, to present their current research, and to discuss topics with other students in order to look for synergies and common research topics. The idea was very successful and the assessment made by the PhD Student was very good. It also helped to achieve one of the major goals of the NESUS Action: to establish an open European research network targeting sustainable solutions for ultrascale computing aiming at cross fertilization among HPC, large scale distributed systems, and big data management, training, contributing to glue disparate researchers working across different areas and provide a meeting ground for researchers in these separate areas to exchange ideas, to identify synergies, and to pursue common activities in research topics such as sustainable software solutions (applications and system software stack), data management, energy efficiency, and resilience.

Prof. Jesus Carretero University Carlos III of Madrid NESUS Chair

February 2016

#### TABLE OF CONTENTS

#### First NESUS PhD Symposium (PhD-NESUS 2016)

- 1 Hossam Zawbaa

- Computational Intelligence Modeling of Pharmaceutical Properties

- 5 Sidi Ahmed Mahmoudi, Pierre Manneback

- Towards a Smart Selection of Multi-CPUMulti-GPU Platforms for Image and Video Processing Algorithms

- 9 Sandra Catalan, Rafael Rodríguez-Sánchez, Enrique S. Quintana-Orti

- Energy aware execution environments and algorithms on low power multi-core architectures

- 13 Samuel Cremer, Michel Bagein, Saïd Mahmoudi, Pierre Manneback

- CuDB: a Relational Database Engine Boosted by Graphics Processing Units

- 17 Andrej Bugajev, Raimondas Ciegis

- The analysis of parallel OpenFOAM solver for the heat transfer in electrical power cables

- 21 Dimitris Tychalas, Helen Karatza

- Cloud resource management

- 25 Adrian Perez Dieguez, Margarita Amor, Doallo Ramón

- Techniques for Autotuning Algorithms on Heterogenous Platforms

- 29 Nuria Losada, María J. Martín, Patricia González

- Resilience of Parallel Applications

- 33 Francisco Javier Alventosa Rueda, Pedro Alonso Jordá, Gemma Piñero Sipan, Antonio Manuel Vidal Macia Beamforming filtering with real-time constraints on mobile embedded devices

- 37 Raluca Maria Aileni, Rodica Strungaru, Carlos Valderrama

- Data mining for autonomous wearable sensors used for elderly healthcare monitoring

- 41 Roman Mego

- Processor Model for the Instruction Mapping Tool

- 45 Ilias Mavridis, Helen Karatza

- Distributed Processing in Cloud Computing

- 49 Daniela Gifu

- The Analysis of Diachronic Variation in Romanian Print Press

- 55 Sergio Iserte, Antonio J. Peña, Rafael Mayo Gual, Enrique S. Quintana-Orti, Vicenç Beltran Dynamic Management of Resource Allocation for OmpSs Jobs

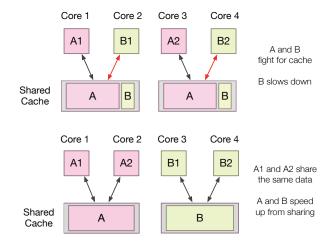

- 59 Germán Ceballos, David Black-Schaffer

- Spatial and Temporal Cache Sharing Analysis in Tasks

- 65 Rafael Sotomayor, Jose Daniel Garcia

- Application Partitioning and Mapping Techniques for Heterogeneous Parallel Platforms

- 69 Alex Becheru

- A Framework for Knowledge Management using Complex Networks Methods

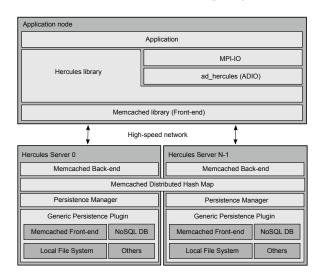

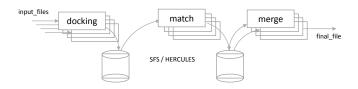

- 73 Francisco Rodrigo Duro, Javier Garcia Blas, Jesus Carretero

- A generic I/O architecture for data-intensive applications based on in-memory distributed cache

77 Cristina Madalina NoaicaMachine Learning Methods Applied to Biometrics

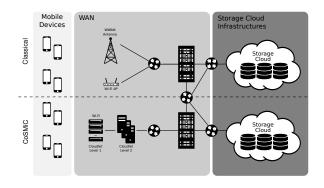

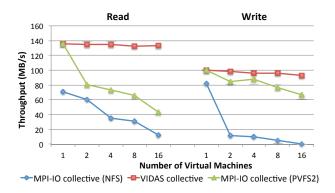

79 Pablo Llopis Sanmillan, Javier Garcia Blas, Florin Isaila

Work in progress about enhancing the programmability and energy efficiency of storage in HPC and cloud environments

#### 85 List of Authors

Hossam Zawbaa 1

# Computational Intelligence Modeling of Pharmaceutical Properties

#### Hossam M. Zawbaa

Faculty of Mathematics and Computer Science, Babes-Bolyai University, Romania Faculty of Computers and Information, Beni-Suef University, Egypt hossam.zawbaa@gmail.com

#### Abstract

In the pharmaceutical industry, a good understanding of the casual relationship between product quality and attributes of formulations is very useful in developing new products, and optimizing manufacturing processes. Feature selection is mandatory due to the abundance of noisy, irrelevant, or misleading features. The selected features will improve the performance of the prediction model and will provide a faster and more cost effective prediction than using all the features. With the big data captured in the pharmaceutical product development practice, computational intelligence (CI) models and machine learning algorithms could potentially be used to identify the process parameters of formulations and manufacturing processes. That needs a deep investigation of roller compaction process parameters of pharmaceutical formulations that affect the ribbons production. In this work, we are using the bio-inspired optimization algorithms for feature selection such as (grey wolf, Bat, flower pollination, social spider, antlion, moth-flame, genetic algorithms, and particle swarm) to predict the different pharmaceutical properties.

Keywords Computational Intelligence, Pharmaceutical Roll Compaction, Bio-inspired Optimization, Feature Selection

#### I. Introduction

A feature is an measurable property of the problem under observation, over the past years the domain of features in machine learning and pattern recognition applications have expanded from tens to hundreds of variables or features used in such applications. Hence the use of reduction or selection techniques is essential to reduce the large number of feature in the problem. Feature selection is a process of selecting a subset of features from a larger set of features, which leads to the reduction of the dimensionality of features space for a successful classification task. Feature selection provides a way for identifying the important features and removing irrelevant or redundant features from a dataset [1]. Feature Selection helps in understanding data, reducing computation requirement, reducing the effect of curse of dimensionality and improving the predictor performance [2].

Formerly, an exhaustive search for the optimal or near to optimal solution in a enormous search space may be impracticable, many researches seek to model the feature selection as a optimization problem [3]. One of the most used methods to solve the feature selection problems are evolutionary and swarm intelligence methods. Swarm intelligence is a computational intelligence-based approach which is made up of a population of artificial agents and inspired by the social behavior of animals (fish, birds, fireflies, etc.) from the real world. Example of such methods are ant colony optimization [4], bat algorithm [5], and particle swarm optimization (PSO) [6].

Roller compaction is method of preparing drug granules for capsules or for tablet formulations used in the pharmaceutical industry with suitable densification. The most common filler binder excipient used in roller compaction are microcrystalline cellulose (MCC), dibasic calcium phosphate (DCP), and lactose. Roller compaction is a particle size enlargement technique that granulated the powder materials to obtain materials of intermediate sizes in tablets production. The use of latest technology facilitates to efficient production of high quality granules. The selection of the critical roll compaction parameters such as (constant compacting pressure and constant roller gap) is very important.

Being a part of the development of in-silico process models for roll compaction (IPROCOM) project, Marie Curie. IPROCOM project employs a multidisciplinary approach to understand the fundamental mechanisms of particulate manufacturing processes involving roll compaction, and to develop predictive in-silico tools that can be used by various industrial sectors in Europe. In addition, we in need to establish a computational intelligence framework that identifies the critical material and process parameters and defines the design spaces for robust formulations and efficient production.

The aggregate aim of this work is to propose the bioinspired optimization algorithms for feature selection that maximize feature reduction and obtaining comparable or even better prediction results of roll compaction parameters from using full features and conventional feature selection techniques.

#### II. RELATED WORK

Evolutionary computational (EC) algorithms have been used in feature selection issues such as genetic algorithm (GA), genetic programming (GP), ant colony optimization (ACO), and particle swarm optimization (PSO). GA was the first evolutionary based algorithm introduced in the literature and developed based on the natural process of evolution through reproduction [7]. Particle swarm optimization (PSO) is one of the well-known swarm algorithms. In PSO, each solution is considered as a particle with specific characteristics (position, fitness, and speed vector) that defines the moving direction of each particle [8]. A hybrid methods can also be applied in which two evolutionary algorithms are used to solve the problem, for example [9] proposed a new feature

selection approach that is based on the integration of GA and PSO. Artificial bee colony (ABC) is a numerical optimization algorithm based on foraging behavior of honeybees. In ABC, the employer bees try to find food source and advertise the other bees. The onlooker bees follow their interesting employer and the scout bee fly spontaneously to find the best food source [10]. Social spider optimization (SSO) algorithm is a population based algorithm and one of the comparatively recent swarm algorithms [11].

A virtual bee algorithm (VBA) is applied to optimize the numerical function in 2-D using a swarm of virtual bees, which move randomly in the search space and interact to find food sources. From the interactions between these bees results the possible solution for the optimization problem [12]. A proposed approach based on natural behavior of honeybees, which randomly generated worker bees are moved in the direction of the elite bee. The elite bee represents the optimal (near to optimal) solution [13]. Ant colony optimization (ACO) wrapper-based feature selection algorithm was applied in network intrusion detection with rough set theory [14]. Artificial fish swarm (AFS) algorithm mimics the stimulant reaction by controlling the tail and fin. AFS is a robust stochastic technique based on the fish movement and its intelligence during the food finding process [15].

#### III. THESIS IDEA

The main goal of this thesis study was to investigate the roller compaction and granulation characteristics of pharmaceutical formulations. During the roller compaction operation, uniformly mixed powder blends are passed continuously through the gap between a pair of counter rotating compression rolls to form solid ribbons or sheets which are then passed through a mill or granulator with a suitable sized screen to form dry granules. Compared to wet granulation processes, dry granulation by roller compaction has various advantages such as simpler manufacturing procedure, easier scale up and higher production throughput. Dry granulation is also energy efficient and suitable for processing pharmaceutical agents that are sensitive to moisture and heat. The complex-

Hossam Zawbaa 3

ity of formulation design is a highly specialised task, requiring specific knowledge and often years of experience. In this work, we have applied bio-inspired optimization algorithms such as (grey wolf optimization, Bat optimization, cuckoo search, flower pollination algorithm, social spider optimization, etc) for feature selection and prediction of different pharmaceutical properties. After that, we use machine learning techniques like (artificial neural network, k-nearest neighbour, extreme learning machine, etc) to predict the different pharmaceutical properties such as (true density, porosity, tensile strength, fines, etc).

Each optimization algorithm is run for 20 times to test the algorithm convergence capability. The used evaluation indicators to compare different optimization algorithms are:

- 1. **Average reduction** represents the average size of selected features to the total number of features.

- 2. **Mean square error (MSE)** measures the average of squared errors that means the difference between actual output and predicted ones.

The two evaluation criteria or objective function in the wrapper feature selection is commonly reflecting the regression performance as well as the feature reduction. A generic representation of the fitness function representing for both regression performance and feature reduction as described in equation (1):

$$f_{\theta} = \alpha * E + (1 - \alpha) \frac{\sum_{i} \theta_{i}}{N}, \tag{1}$$

where  $f_{\theta}$  is the fitness function given a vector  $\theta$  sized N with 0/1 elements representing unselected / selected features, N is the total number of features in the dataset, E is the prediction error, and  $\alpha$  is a constant controlling the importance of regression performance to the number of features selected.

A random controlling term ( $\alpha$ ) is used to balance the trade-off between exploration and exploitation and hence should be carefully adapted. Therefore, at the beginning of optimization ( $\alpha$ ) has its maximum value to allow for maximum exploration and at the end of optimization it has minimum value for more exploitation of search space. Each bio-inspired algorithm is

initialized with n random agents, each agent (solution) representing a given selected feature combination. After that, each algorithm is iteratively applied for a number of iterations hoping to converge to a good solution. Individual solution is represented as a continuous valued vector with same dimension as number of attributes in the given dataset. The solution vector continuous values are limited to the range [0, 1]. At the solution fitness function evaluation the continuous valued solution is threshold to its binary representation using equation (2).

$$y_{ij} = \begin{cases} 0 \text{ If}(x_{ij} < 0.5) \\ 1 \text{ Otherwise} \end{cases}$$

(2)

where  $x_{ij}$  is the continuous value of the solution number i in dimension j, and  $y_{ij}$  is a discrete representation of solution vector x.

#### IV. Conclusion and future work

In this work, bio-inspired optimization algorithms were proposed and applied for feature selection in wrapper mode. The most recent bio-inspired optimization algorithms such as (GWO, ALO, BAT, SSO, and FPA) are hired in the feature selection domain for evaluation and results are compared against well-known feature selection methods particle swarm optimization (PSO) and genetic algorithm (GA). The evaluation is performed using a set of evaluation criteria to assess different aspects of the proposed system.

#### ACKNOWLEDGMENT

This work was supported by the IPROCOM Marie Curie initial training network, funded through the People Programme (Marie Curie Actions) of the European Union's Seventh Framework Programme FP7/2007-2013/ under REA grant agreement No. 316555. In addition, this work was partially supported by NESUS.

#### References

- [1] Chizi, Barak and Rokach, Lior and Maimon, Oded and Wang, J, "A Survey of Feature Selection Techniques", 2009.

- [2] Chandrashekar, Girish, Sahin, Ferat, "A survey on feature selection methods", Computers & Electrical Engineering, pp. 16-28, Vol. 40, No. 1, 2014.

- [3] Duda, Richard O and Hart, Peter E and Stork, David G, "Pattern classification", John Wiley & Sons, 2012.

- [4] Forsati, Rana and Moayedikia, Alireza and Jensen, Richard and Shamsfard, Mehrnoush and Meybodi, Mohammad Reza, "Enriched ant colony optimization and its application in feature selection", Neurocomputing, pp. 354-371, Vol. 142, 2014.

- [5] Rodrigues, Douglas and Pereira, Luís AM and Nakamura, Rodrigo YM and Costa, Kelton AP and Yang, Xin-She and Souza, André N and Papa, João Paulo, "A wrapper approach for feature selection based on Bat Algorithm and Optimum-Path Forest", Expert Systems with Applications, pp. 2250-2258, Vol. 41, No. 2, 2014.

- [6] Inbarani, H Hannah, Azar, Ahmad Taher, Jothi, G, "Supervised hybrid feature selection based on PSO and rough sets for medical diagnosis", Computer methods and programs in biomedicine, pp. 175-185, Vol. 113, No. 1, 2014.

- [7] Adaptation in natural and artificial systems: an introductory analysis with applications to biology, control, and artificial intelligence, John Henry Holland, MIT press, 1992.

- [8] R. C. Eberhart, and J. Kennedy, "A New Optimizer Using Particle Swarm Theory", Proceeding of the Sixth International Symposium on Micro Machine and Human Science, Nagoya, Japan, pp. 39-43, 1995.

- [9] Ghamisi, Pedram and Benediktsson, Jon Atli, "Feature selection based on hybridization of ge-

- netic algorithm and particle swarm optimization", Geoscience and Remote Sensing Letters, IEEE, pp. 309-313, Vol. 12, No. 2, 2015.

- [10] Dervis Karaboga, Bahriye Basturk, "A powerful and efficient algorithm for numerical function optimization: artificial bee colony (ABC) algorithm", Journal of Global Optimization, Vol. 39, No. 3, pp. 459-471, 2007.

- [11] Cuevas, E., Cienfuegos, M., Zaldivar, D., Perez-Cisneros, M., "A swarm optimization algorithm inspired in the behavior of the social-spider", Expert Systems with Applications, Vol. 40, No. 16, pp. 6374-6384, 2013.

- [12] Yang XS, "Engineering optimizations via natureinspired virtual bee algorithms", In: Lecture notes in computer science, Springer (GmbH), pp. 317-323, 2005.

- [13] Sundareswaran K, Sreedevi VT, "Development of novel optimization procedure based on honey bee foraging behavior", IEEE International conference on systems, man and cybernetics, pp. 1220-1225, 2008.

- [14] H. Ming, "A rough set based hybrid method to feature selection", in Proc. Int. Symp. KAM, pp. 585-588, 2008.

- [15] X. L. Li, Z. J. Shao, J. X. Qian, "An Optimizing Method Based on Autonomous Animates: Fish-swarm Algorithm", Methods and Practices of System Engineering, pp. 32-38, 2002.

# Towards a Smart Selection of Hybrid Platforms for Multimedia Processing

#### SIDI AHMED MAHMOUDI AND PIERRE MANNEBACK

University of Mons, Belgium sidi.mahmoudi@umons.ac.be

#### Abstract

Nowadays, images and videos have been present everywhere, they can come directly from camera, mobile devices or from other peoples that share their images and videos. The latter are used to illustrate different objects in a large number of situations. This makes from image and video processing algorithms a very important tool used for various domains related to computer vision such as video surveillance, medical imaging and database (images and videos) indexation methods. The performance of these algorithms have been so reduced due the the high intensive computation required when using new image and video standards. In this paper, we propose a new framework that allows users to select in a smart and efficient way the processing units (GPU or/and CPU) within heterogeneous systems, when treating different kinds of multimedia objects: single image, multiple images, multiple videos and video in real time. The framework disposes of different image and video primitive functions that are implemented on GPU, such as shape (silhouette) detection, motion tracking using optical flow estimation, edges and corners detection. We have exploited these functions for several situations such as indexing videos, segmenting vertebrae in in X-ray and MR images, detecting and localizing event in multi-user scenarios. Experimentation showed interesting accelerations ranging from 6 to 118, by comparison with sequential implementations. Moreover, the parallel and heterogeneous implementations offered lower power consumption as a result for the fast treatment.

Keywords GPU, Heterogeneous architectures, Image and video processing, Medical imaging, Motion tracking

#### I. Introduction

Recently, the architecture of CPUs has so changed and evolved that the number of integrated computing units has been multiplied. This evolution is reflected in both general (CPU) and graphic (GPU) processors which present a large number of computing units, their power has far exceeded the CPUs ones. In this context, image and video processing algorithms are well adapted for acceleration on the GPU by exploiting its processing units in parallel, since they are mainly based on applying the same computation over many points or pixels. Many GPU and parallel computing approaches have been developed recently. Although they present a great power of GPU architecture, any is able to process high definition image and video efficiently and accordingly to the type of Medias (single image, multiple

image, multiple videos and video in real time). Thus, there was a need to develop a framework capable of addressing the outlined problem. In literature, we can categorize two types of related works based on the exploitation of parallel and heterogeneous platforms for multimedia processing: one related to image processing on GPU such as presented in [1], [2] which proposed GPU implementations that use CUDA <sup>1</sup> for basic image processing and medical imaging algorithms. A performance evaluation of GPU-based image processing algorithms is presented in [3]. These implementations offered high improvement of performance thanks to the exploitation of the GPU's computing units in parallel. However, these accelerations are so reduced when processing image databases with different resolutions. Thus, an efficient exploitation of CPU, GPU and

<sup>&</sup>lt;sup>1</sup>CUDA. https://developer.nvidia.com/cuda-zone

hybrid (Multi-CPU/Multi-GPU) platforms is needed with an effective management of the related memories. Notice also that the processing of images with low resolutions cannot benefit from the high power of GPUs since few computations will be launched. This implies an analysis of algorithms complexities before their parallelization. On the other hand, video processing algorithms require generally a real-time treatment. We may find several methods in this category, such as understanding human behavior, event detection, camera motion estimation, etc. These methods apply mainly motion tracking algorithms that can exploit several techniques such as optical flow estimation [4], block matching technique [5], and scale-invariant feature transform (SIFT) [6] descriptors. In this case also, several GPU implementations have been proposed for sparse [7] and dense [8] optical flow computation.

#### II. RESEARCH IDEA

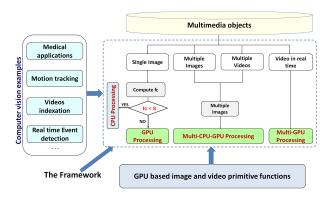

Despite the high speedups presented in the previous section, none of the above-mentioned implementations can provide real-time processing of high definition videos. Therefore, we propose a new framework that allows a smart, effective and adapted processing of different type of Medias exploiting parallel and heterogeneous platforms. This framework enables to select the units (GPU or/and CPU) for processing, and also the related implementations to be applied. The latter are selected after checking the type of media to treat and the algorithm complexity. The framework offers several scheduling strategies that allow an equivalent distribution of tasks over the available processors. The data transfer times are also reduced as a result of the efficient management of GPU memories and to the overlapping (CUDA streaming) of data copies by kernels executions. Otherwise, the framework disposes of several GPU-based image and video primitive functions, such as shape detection, motion tracking using optical flow estimation, edges and corners extraction. We have exploited these functions for several situations such as indexing videos, segmenting vertebrae in Xray and MR images, detecting and localizing event in multi-user scenarios. The primitive functions are presented in detail in our previous publication [9]. Figure 1 illustrate the proposed framework, presenting different applications that can exploit in an adapted way the heterogeneous systems, which offers a low energy consumption as a result for the fast and accelerated treatment. The main contributions of our framework can be summarized within five points:

- Smart selection of resources (CPU or/and GPU) based on the estimated complexity and the type of media. Additional computing units are exploited only in case of intensive and tasks;

- 2. Several image and video GPU primitive functions;

- 3. Efficient scheduling of tasks and management of memories in case of heterogeneous computation;

- Acceleration of real-time image and video processing applications;

- 5. low energy consumption.

Figure 1: Multi-CPU/Multi-GPU based Framework for Multimedia Processing

#### III. EXPERIMENTAL RESULTS

The proposed framework has been exploited in several high intensive applications related to image and video processing such as vertebra segmentation, videos indexation, event detection and localization, etc.

#### III.1 Heterogeneous vertebra segmentation

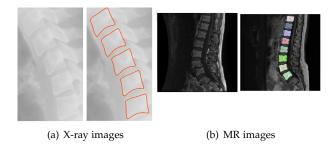

The main objective of this method is the cervical vertebra mobility analysis on X-Ray or MR images. The aim is to detect vertebra automatically. The computation time presents one of the most important requirements for this application. Based on our framework, we propose a hybrid implementation of the most intensive steps, which have been defined within our estimation complexity equation [9]. Our solution for vertebra detection on Multi-CPU/Multi-GPU platforms is detailed in [10] for X-Ray images, and in [11] for MR images. Fig. 2(a) presents the results of vertebra detection in X-ray images, while Fig. 2(b) is related to present the detected vertebra in MR images. Notice that the use of heterogeneous platforms allowed to improve performance with a speedup of  $30 \times$  for vertebra detection within 200 high resolution (1472×1760) X-ray images, and a speedup of 118 × when detecting vertebra in a set of 200 MR images (1024×1024).

Figure 2: Vertebra detection in X-ray and MR images

## III.2 Multi-CPU/Multi-GPU based videos indexation

The context of this application is to develop a new browsing environment for images and videos databases. This method consists on calculating similarities between videos sequences (composed of consecutive images), based on detecting the feature of images (frames) that compose videos [12]. The main drawback of this application is the high computing time that increases considerably when enlarging videos databases

and definitions. Using our framework, we developed a hybrid version of the most intensive step of the features extraction process. This step, detected within our complexity estimation equation defined in [9], consists of contours extraction algorithm that provides relevant information for localizing motion's areas. This implementation is detailed in [13] showing a total gain of 80%, compared to the total time of the sequential version, when treating 800 frames of a video sequence (1080x720).

### III.3 Multi-GPU based Event detection and localization in real time

The aim of this method is to detect and localize events in video sequences in real time. The method is based on modeling normal behaviors, and then estimating the difference between the normal behavior model and the observed events of behaviors. The detected variations are labeled as emergency events, and the deviations from examples of normal behavior are used to characterize abnormality. After the detection of each event, we localize the related areas in video frames where motion behavior is surprising compared to the rest of motion. Using our framework, we developed a Multi-GPU version of the most intensive steps of the application. The latter are detected within our complexity estimation equation defined in [9]. This implementation is detailed in [14]. Notice that performed tests show that our application can turn in multi-user scenarios, and in real time even when processing high definition videos such as Full HD or 4K standards. The scalability of our results is also achieved thanks to the effective exploitation of multiple GPUs. A demonstration of GPU based features detection, features tracking, and event detection in crowd video is shown in this video sequence: https://www.youtube.com/watch?v=PwJRUTdQWg8.

#### IV. CONCLUSION AND FUTURE WORK

We proposed in this paper a new framework that allows a smart and efficient exploitation of Multi-CPU/Multi-GPU platforms accordingly to the type of multimedia (single image, multiple images, multiple videos, video in real time) objects. This framework

enables to select the units (GPU or/and CPU) for processing, and also the related implementations to be applied. The latter are selected after checking the type of media to treat and the algorithm complexity. Experimental results showed different use case applications that have been improved thanks to our framework. Each application has been integrated in an adapted way for exploiting resources in order to reduce both computing time and energy consumption. As future work, we plan to port our algorithms on GPU Tegra Mobile Processors <sup>2</sup> that allow to reduce significantly the power consumption, with maintaining high performance of computation.

#### Acknowledgment

Authors would like to thank the support of European COST NESUS action IC1305 " Network for Sustainable Ultra-scale Computing"

#### REFERENCES

- [1] Yang. Z and Zhu. Y and pu. Y, "Parallel Image Processing Based on CUDA" HPCCE Workshop, IEEE International Conference on Cluster Computing, pp. 198-201, 2008.

- [2] Mahmoudi. Sidi Ahmed and Lecron. F and Manneback. P and Benjelloun. M and Mahmoudi. S, " GPU-Based Segmentation of Cervical Vertebra in X-Ray Images " HPCCE Workshop, IEEE International Conference on Cluster Computing, pp. 1-8, 2010.

- [3] Park. Kyu and Nitin. Singhal and Man. Hee Lee, "Design and Performance Evaluation of Image Processing Algorithms on GPUs" *IEEE Transactions* on Parallel and Distributed Systems, vol. 28, pp. 1-14, 2011.

- [4] Horn. B. K and Schunk. B. G, "Determining Optical Flow "Artificial Intelligence, vol. 2, pp. 185-203, 1981.

- [5] Shan Zhu and Kai-Kuang Ma, "A new diamond search algorithm for fast block-matching motion estimation" *IEEE Transactions on Image Processing*, vol. 9, pp. 287-290, 2000.

- [6] Lowe. D. G, "Distinctive image features from scale-invariant keypoints" *International Journal of Computer Vision (IJCV)*, vol. 60(2), pp. 91-110, 2004.

- [7] Mahmoudi. Sidi Ahmed and Kierzynka. Michal and Manneback. Pierre and Kurowski. K, "Realtime motion tracking using optical flow on multiple GPUs "Bulletin of the Polish Academy of Sciences: Technical Sciences, vol. 62, pp. 139-150, 2014.

- [8] Marzat. J and Dumortier. Y and Ducrot. A, "Realtime dense and accurate parallel optical flow using CUDA" *In Proceedings of WSCG*, pp. 105-111, 2009.

- [9] Mahmoudi. Sidi Ahmed and Manneback. Pierre, " Multi-CPU/Multi-GPU Based Framework for Multimedia Processing " Computer Science and Its Applications, vol. 456, pp. 54-65, 2015.

- [10] Lecron. Fabian et al., "Heterogeneous Computing for Vertebra Detection and Segmentation in X-Ray Images "International Journal of Biomedical Imaging: Parallel Computation in Medical Imaging Applications, vol. 2011, pp. 1-12, 2011.

- [11] Larhmam. Mohammed Amine et al., "A Portable Multi-CPU/Multi-GPU Based Vertebra Localization in Sagittal MR Images", *International Conference on Image Analysis and Recognition, ICIAR* 2014, pp. 209-218, 2014.

- [12] Damien Tardieu et al., "Video Navigation Tool: Application to browsing a database of dancers' performances", *QPSR of the numediart research program*, vol. 2, number. 3, pp. 85-90, 2009.

- [13] Mahmoudi Sidi Ahmed and Manneback Pierre, "

Efficient exploitation of heterogeneous platforms for images features extraction " 3rd International Conference on Image Processing Theory, Tools and Applications (IPTA), pp. 91-96, 2012.

- [14] Mahmoudi Sidi Ahmed and Manneback Pierre, " Multi-GPU based event detection and localization using high definition videos " *International Confer*ence on Multimedia Computing and Systems (ICMCS), pp. 81-86, 2014.

<sup>&</sup>lt;sup>2</sup>Tegra Mobile Processors: http://www.nvidia.com/object/tegra.html

# Energy aware execution environments and algorithms on low power multi-core architectures

Sandra Catalán, Rafael Rodríguez-Sánchez, Enrique S. Quintana-Ortí

Universitat Jaume I, Spain catalans@uji.es, rarodrig@uji.es, quintana@uji.es

#### **Abstract**

Energy consumption is a key aspect that conditions the proper functioning of nowadays data centers and high performance computing just like the launch of new services, due to its environmental negative impact and the increasing economic costs of energy.

The energy efficiency of the applications used in these data centers could be improved, especially when systems' utilization rate is low or moderate, or when targeting memory bounded applications. In this sense, energy proportionality stands for systems which power consumption is in line with the amount of work performed in each moment. As a response to these needs, the main objective of this project is to study, design, develop and analyze experimental solutions (models, programs, tools and techniques) aware of energy proportionality for scientific and engineering applications on low-power architectures. With the aim of showing the benefits of this contribution, two applications, coming from the image processing and dynamic molecular simulation fields, have been chosen.

Keywords Energy, low-power architectures, linear algebra, NESUS

#### I. MOTIVATION

Nowadays there is a vast variety of scientific, industrial and engineering applications that have great computing power and storage requirements, and their demand is still growing. In order to obtain more precise solutions in these applications, scientists need to build and work with sophisticated physical and mathematical models. Scientific computation (seen as the elaboration of mathematical models and the use of computers to analyze and solve scientific problems) is an efficient tool to make scientific discoveries that are complementary to the most traditional methods based on theory and experimentation [1] As a consequence, new data processing systems and high performance computing centers collapse just a few weeks later from their commissioning [2].

To face the mathematical formulation at the bottom of the physical laws advanced numerical algorithms are required: linear algebra, spectral methods (e.g, FFT), N-body methods, mesh methods to solve partial differential equations, as well as searching, classification and optimization algorithms, among others [2] are required. In particular, the main part of the compu-

tations demanded to solve these scientific, industrial and engineering applications can be decomposed into a reduced number of well known matrix computation problems, e.g., simple operations of linear algebra, linear equation systems, minimum least square problems, eigenvalue and eigenvector problems. In this way, the efficiency of these computation problems determine as a last resort the effectiveness of the software application.

Large scale HPC (high performance computing) systems are great energy consumers, using computing resources and auxiliary systems to work [1]. This energy consumption has a direct impact on the operation costs and maintenance of the computing centers, threatening their existence and complicating the acquisition of new facilities. However, electricity cost is not the only problem; energy consumption results in carbon dioxide emissions dangerous to the environment and public health, and the heat reduces the reliability of the hardware components [3].

HPC centers' pressure forced hardware manufacturers to improve their designs to get better energy efficiency: CPU, memory and disks (the main energy consumers in a system, followed by the network and

the power supply unit) provide some energy saving strategies, based on the system transition to a low power consumption state or the dynamic adaptation of frequency and voltage (DVFS or Dynamic Voltage Frequency Scaling) [4]. On the other hand, software systems, communication libraries and, specially, computational libraries and application codes used in HPC centers have been, traditionally, unaware of power consumption. In fact, the Top500 [5] list is a good example. Computers listed in this ranking are classified depending on their sustained performance (in FLOPS) when running the Linpack test (basically, solving a dense linear system of scalable dimension). However, the numerical method behind this test, LU factorization, is far from being representative for most real scientific codes [6].

Despite the great benefits [7] that HPC energy aware solutions can provide in terms of run time optimization and energy conservation, this topic is still at an early research stage if compared with energy study in other segments. Recently, HPC community has presented energy aware metrics, e.g., Energy Delay Product (EDP), Energy To Solution (ETS), FLOPS/Watt or FTTSE [8], that are becoming more significant when evaluating algorithms and computers performance. In fact, the Green500 [9] ranking, which uses these metrics to compare and classify supercomputers all around the world regarding their energy efficiency, is becoming more considered every day.

#### II. Related work

Nowadays HPC linear algebra libraries make use of hardware concurrency in multi-core processors using multi-threaded implementations highly optimized for a small set of linear algebra kernels (particularly, BLAS matrix-vector product and matrix-matrix product). For years, this approach was successfully followed by the scientific community, since it provides an interface that has allowed the development of complex and architecture independent packages of numerical methods with portable performance. However, with the increasing number of cores (e.g, Intel Xeon Phi), this solution became suboptimal due to the fact that concurrency at BLAS level implies a high number of thread synchronizations, causing a high overhead.

Recently, many projects demonstrated the benefits of applying parallelism at a higher level, in both dense and sparse linear algebra, through applications that decompose operations in fine grain tasks, with outof-order execution by means of an scheduling aware of the tasks' dependencies. Examples of this successful solution are libflame (SuperMatrix [10]), PLASMA (Quark) [11], SMPSs [12], StarPU [13], etc., based on the ideas/techniques firstly proposed by the project Cilk [14] of MIT. These execution frameworks aim at the gross performance as final value for the user. However, they are completely energy unaware. Initial research efforts showed the possibility of keeping isoefficiency/isoscalability in a parallel solver while getting low power consumption, and the benefits derived from this approach. This can be done, for instance, scheduling non-critical tasks to less powerful and low power consumption cores (on heterogeneous environments) or through processor frequency adjustment, and promoting idle cores to low power states [15, 16, 17].

Previously mentioned solutions try to efficiently identify and make use of task parallelism in software applications. To this end, they provide the user with an explicit or implicit mechanism to identify tasks and dependencies among them. There is a part in this framework that builds a Directed Acyclic Graph (DAG) that gathers all the dependencies, and this information is used by the scheduler, which in turn issues tasks to execution when their dependencies are solved and there are enough free computational resources. Some of these frameworks also tackle the existence of multiple address spaces, providing the programmer with an explicit transfer mechanism or, alternatively, a memory control mechanism built in the scheduler that performs transparent transfers for the programmer. Scheduling algorithms at the bottom of these execution frameworks aim at optimizing performance, but generally, they do not consider energy as a variable to make decisions. However, for some operations, it is possible to improve energy efficiency during the dynamic execution of a DAG if some non-critical tasks are executed at a lower speed (via, e.g., the frequency reduction of cores applying DVFS).

On the way towards the construction of exaflop supercomputers, some research lines stand for the utilization of highly heterogeneous systems, composed of some nodes, with a huge amount of simple and low-power multi-core processors, combined with some other nodes, featuring hardware accelerators [18]. In the same vein, some recent works reveal energy advantages when using low-power processors, such as Intel Atom, ARM A-15, or more specialized systems, like ARM+NVIDIA Carma, composed of an ARM A-9 processor and a small Quadro 1000M GPU, or the Digital

Signal Processors (DSP) of Texas Instruments [19, 20].

#### III. THESIS IDEA

The main objective of the research proposal is to study, design, develop and experimentally analyze solutions that are aware of the energy proportionality (models, programs, tools and techniques) of scientific and engineering applications running on low-power architectures. This objective is composed of two specific targets:

- Studying, characterizing and modeling low-power architectures' performance and energy efficiency, which include, Intel Atom, ARM Cortex-A15, Texas Instruments DSP C66x, among others.

- Designing, developing and evaluating energy proportional solutions for scientific applications in the field of hyperspectral image processing and macromolecular simulations.

So far the improvement of these kind of applications was focused on increasing their performance, through traditional parallel systems that were to a large extent energy proportionality oblivious. The novelty of this proposal is founded on the study of specific HPC techniques for low-power architectures, capable of making the best of the greater energy proportionality of these systems.

To achieve the proposed goal, the first stage of the work will consist of analyzing, modeling and optimizing basic kernels on low-power architectures. To this end, a representative number of low-power architectures will be selected in order to build experimental energy models with an appropriate collection of parameters and to determine computing and memory access costs in terms of energy. In addition, the same basic kernels will be used to characterize the energy consumption of the different components in a given architecture. After this initial study, the improvement of hyperspectral image processing problems and macromolecular simulations will be tackled. In both cases, the exploitation of parallelism at different levels (fine grain, gross grain and task parallelism) and the use of the MPI paradigm will be key to get the best of these applications on low-power architectures.

#### IV. Conclusion and future work

Apart from the computational implications explained along this text, from the economical and digital society point of view, this proposal is also part of the greenhouse gas reduction challenge and the energy efficiency goal. Moreover, this project is strongly connected with the climate change action and the use of raw materials and natural resources. On the other hand, the macromolecular simulations, and to a large extent also the hyperspectral image processing, make use of and produce huge amounts of data/results. Consequently, these two kind of applications belong to the "big data" category, being also characterized as a priority topic by the economical and digital society challenges.

As future work, the improvement of dense linear algebra operations (focused on the BLIS library [21]) on low-power architectures has to be completed and the improvement of hyperspectral image processing problems and macromolecular simulations need to be performed.

#### Acknowledgment

This work is partially supported by EU under the COST Program Action IC1305: Network for Sustainable Ultrascale Computing (NESUS) and the FPU program of MECD.

#### REFERENCES

- [1] J. Dongarra, *et al*, The international ExaScale software project roadmap, Int. J. of High Performance Computing & Applications 25 (1) (2011) 3–60.

- [2] International technology roadmap for semiconductors, http://www.itrs.net/(2013).

- [3] W.-c. Feng, X. Feng, R. Ge, Green supercomputing comes of age, IT Professional 10 (1) (2008) 17 –23. doi:10.1109/MITP.2008.8.

- [4] W. Y. Lee, Energy-saving DVFS scheduling of multiple periodic real-time tasks on multi-core processors, in: Distributed Simulation and Real Time Applications, 2009. DS-RT '09. 13th IEEE/ACM International Symposium on, 2009, pp. 216 –223. doi:10.1109/DS-RT.2009.12.

- [5] The Top 500 list, http://www.top500.org/ (2014).

- [6] P. Kogge, K. Bergman, S. Borkar, D. Campbell, W. Carlson, W. Dally, M. Denneau, P. Franzon, W. Harrod, J. Hiller, S. Karp, S. Keckler, D. Klein,

- R. Lucas, M. Richards, A. Scarpelli, S. Scott, A. Snavely, T. Sterling, R. S. Williams, K. Yelick, ExaScale computing study: Technology challenges in achieving ExaScale systems (2008).

- [7] S. Albers, Energy-efficient algorithms, Commun. ACM 53 (2010) 86–96.

- [8] C. Bekas, A. Curioni, A new energy aware performance metric, Computer Science Research and Development 25 (2010) 187–195.

- [9] The Green 500 list, http://www.green500.org/ (2014).

- [10] E. Chan, F. G. Van Zee, P. Bientinesi, E. S. Quintana-Ortí, G. Quintana-Ortí, R. van de Geijn, SuperMatrix: A multithreaded runtime scheduling system for algorithms-by-blocks, in: ACM SIGPLAN 2008 symposium on Principles and practices of parallel programming (PPoPP'08), 2008, to appear.

- [11] F. Song, S. Tomov, J. Dongarra, Enabling and scaling matrix computations on heterogeneous multi-core and multi-gpu systems, in: Proceedings of the 26th ACM International Conference on Supercomputing, ICS '12, ACM, New York, NY, USA, 2012, pp. 365–376, http://doi.acm.org/10. 1145/2304576.2304625. doi:10.1145/2304576. 2304625.

- [12] R. M. Badia, J. R. Herrero, J. Labarta, J. M. Pérez, E. S. Quintana-Ortí, G. Quintana-Ortí, Parallelizing dense and banded linear algebra libraries using SMPSs, Conc. and Comp.: Pract. and Exper. 21 (2009) 2438–2456.

- [13] R. M. Badia, J. R. Herrero, J. Labarta, J. M. Pérez, E. S. Quintana-Ortí, G. Quintana-Ortí, Parallelizing dense and banded linear algebra libraries using smpss, Concurrency and Computation: Practice and Experience 21 (18) (2009) 2438–2456.

- [14] R. D. Blumofe, C. F. Joerg, B. C. Kuszmaul, C. E. Leiserson, K. H. Randall, Y. Zhou, Cilk: An efficient multithreaded runtime system, Vol. 30, ACM, 1995.

- [15] P. Alonso, M. F. Dolz, F. D. Igual, R. Mayo, E. S. Quintana-Ortí, DVFS-control techniques for dense linear algebra operations on multi-core processors, Computer Science - Research and

- Development 1-10http://dx.doi.org/10.1007/s00450-011-0188-7.

- [16] P. Alonso, M. F. Dolz, R. Mayo, E. S. Quintana-Ortí, Saving energy in the LU factorization with partial pivoting on multi-core processors, 2012, to appear.

- [17] P. Alonso, M. Dolz, R. Mayo, E. Quintana-Ortí, Improving power efficiency of dense linear algebra algorithms on multi-core processors via slack control, Proc. Int. Conf. High Performance Computing & Simulation–HPCS (2011) 463–470.

- [18] Mont-blanc project, http://www.montblanc-project.eu/(2013).

- [19] J. I. Aliaga, H. Anzt, M. Castillo, J. C. Fernández, G. León, J. Pérez, E. S. Quintana-Ortí, Performance and energy analysis of the iterative solution of sparse linear systems on multicore and manycore architectures, Springer, 2014.

- [20] M. Castillo, J. Fernández, F. Igual, A. Plaza, E. Quintana-Ortí, A. Remón, Hyperspectral unmixing on multicore DSPs: Trading off performance for energy, Selected Topics in Applied Earth Observations and Remote Sensing, IEEE Journal of DOI:10.1109/JSTARS.2013.2266927.

- [21] F. G. Van Zee, R. A. van de Geijn, BLIS: A framework for generating BLAS-like libraries, ACM Trans. Math. Soft.To appear. http://www.cs.utexas.edu/.

# **CuDB:** a Relational Database Engine Boosted by Graphics Processing Units

SAMUEL CREMER, MICHEL BAGEIN, SAÏD MAHMOUDI, PIERRE MANNEBACK

University of Mons, Belgium samuel.cremer@heh.be,michel.bagein@umons.ac.be, said.mahmoudi@umons.ac.be,pierre.manneback@umons.ac.be

#### Abstract

GPUs benefit from much more computation power with the same order of energy consumption than CPUs. Thanks to their massive data parallel architecture, GPUs can outperform CPUs, especially on Single Program Multiple Data (SPMD) programming paradigm on a large amount of data. Database engines are now everywhere, from different sizes and complexities, for multiple usages, embedded or distributed; in 2012, 500 million of SQLite active instances were estimated over the world. Our goal is to exploit the computation power of GPUs to improve performance of SQLite, which is a key software component of many applications and systems. In this paper, we introduce CuDB, a GPU-boosted in-memory database engine (IMDB) based on SQLite. The SQLite API remains unchanged, allowing developers to easily upgrade database engine from SQlite to CuDB even on already existing applications. Preliminary results show significant speedups of 70x with join queries on datasets of 1 million records. We also demonstrate the "memory bounded" character of GPU-databases and show the energy efficiency of our approach.

Keywords Relational Database, In-Memory, SQLite, GPU

#### I. Instruction

One of the most common components in many applications is related to database management. Compared to explicit data management (like C/C++ container), the main advantage of a relational database engine is its flexibility in data storage and manipulation. Relational databases are used in enterprise systems (ERP, CRM), in e-business applications (Apache, MySQL, PHP), in many personal applications (FireFox, Skype, GoogleGears, etc.), in embedded systems (iPhone and low cost cellular phones), and also as a native component in OS (e.g. Android and Symbian). With currently more than a billion copies of implementation, SQLite is probably currently the most widely deployed SQL database engine.

In 2004, a first attempt was made to process some database operations with a GPU [1]. At that time, the GPU architectures were not sufficient mature for

general-purpose processing. GPGPU frameworks appeared much later. Since the first releases in 2007 of the CUDA framework and in 2009 for the OpenCL framework, it has become common to use GPUs in HPC environments for boosting scientific simulations. Nevertheless, GPUs are not commonly used for boosting database engines. Our goal is to show that a GPU-boosted relational database engine can provide drastic speedups while improving energy efficiency. In this paper we briefly introduce CuDB, a GPU boosted version of SQLite.

#### II. RELATED WORKS

In 2007 appeared GPUQP [2], one of the first experimental relational query processing engine working on a Graphics Processing Unit. With GPUQP, each operator of generated query plans could be processed either on CPU or GPU. The source code did not offi-

cially evolve since 2009 but it contributes to provide a reference database engine for many other contributions. In 2010, two researchers proposed Sphyraena [3], a GPU boosted version of SQLite. Unlike other solutions, Sphyraena does not split the query plans into sequences of parallel primitives which require multiple kernel calls. With Sphyraena, the whole query plan is processed on GPU with a single kernel call. Those previous researches have motivated us to start our own GPU-sided relational database engine. We described some specificities of our GPU-sided database, named CuDB, in a previous paper [4].

Meanwhile other teams started different types of researches, with GPU-database engines as central thematic. Sphyraena was used as base for Virginian [5], with as aim the development of a GPU-adapted table-structure. A group of researchers decide to study the impact of transaction mechanisms within GPU-databases and published the experimental GPUTx engine [6]. The main drawback of GPUTx is that it executes only pre-compiled procedures. Another experimental project is GPUDB [7] which was mainly build to run the Star Schema Benchmark. GPUDB has contributed to prove potential performances of GPU-databases with a reference benchmark.

Another group of researchers wanted to create a database engine which is able to run on different hardware architectures. They used GPUQP as reference engine, and developed the OmniDB [8] engine. The experimental CoGaDB [9] database engine allow the generation of query-plans which are dynamically adapted to the target hardware. Unlike most of previous cited solutions, the online available source code is currently still updated.Note also that two commercial solutions of GPU-sided database engines currently exist [10, 11] and a third database engine just started beta phases [12]. Those commercial solutions are more designed for Geographic Information Systems and the Big Data market. They do not encounter all the issues of a full relational DBMS.

#### III. THESIS IDEA

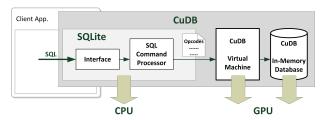

Before explaining the internel architecture of CuDB, it is necessary to understand how our reference engine, SQLite, works. SQLite is subdivided into 4 modules:

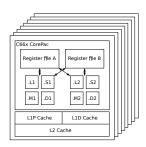

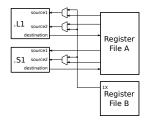

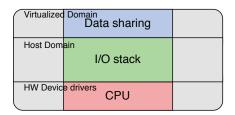

(1) the interface which receive SQL queries, (2) SQL Command Processor which parses the queries and generates query plans, (3) Virtual Database Engine which executes the query plans, and (4) the database. Current version of CuDB engine preserves SQLite API and Command Processor. With CuDB, the Virtual Database Engine and the Database are replaced by our GPU versions. The CPU unit is in charge of parsing queries and translating it into query plans in the first two modules. A query plan is formed by a sequence of opcodes to be processed by a Virtual Machine. Our Virtual Machine is natively designed for GPU parallel architecture as well as our In-Memory Database Engine. This hybrid design was motived by several points: parsing and processing could not expect high speedup although process and storage operation on data can largely benefit of SIMD GPU architectures (several hundreds of synchronized cores). Figure 1 shows the internal architecture of CuDB.

Figure 1: Internal architecture of CuDB.

CuDB engine preserves the original SQLite API, enabling fast, easy and efficient update of existing applications with minor source code updates. To take benefit of the high computation power of GPUs, with GPU-sided virtual machine, each GPU-thread processes the same query plan on its own records, allowing significant speedups with large datasets.

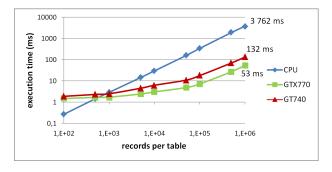

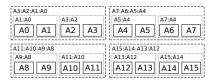

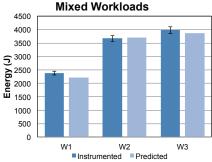

In 2013, a paper specific to the implementation of *SELECT WHERE* and *SELECT JOIN* queries with a GPU-database engine was published [13]. The chosen approach, for the implementation of join operations, was a trivial Cartesian product of tables, which procures a quadratic time complexity. With our engine, we preferred to use a temporary indexation structure for the processing of join-queries, which procure a quasilinear time complexity. We made performance tests with JOIN queries on two non-indexed tables that are

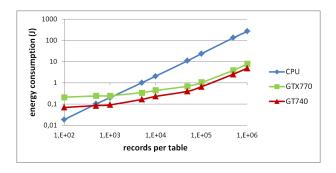

composed by multiple numerical columns. The selectivity of the queries starts at 10% for small datasets and decreases to 0.1% for the one million row tables. Tables count both the same amount of records. We compared the execution time of CuDB, with a standard SQLite CPU implementation in which tables are stored in RAM memory. The specificities of the hardware we used for this performance evaluation are shown on table 1. Figure 2 shows the average execution time of the multiple join queries.

|           | CPU           | GPU1   | GPU2    |

|-----------|---------------|--------|---------|

| Reference | Core i7 2600K | GT740  | GTX770  |

| Units     | 4 + HT        | 384    | 1536    |

| Frequency | 3.8GHz        | ~1GHz  | ~1GHz   |

| Bandwidth | 21GB/s        | 80GB/s | 224GB/s |

Table 1: Hardware specificities

Figure 2: Average execution times with JOIN queries.

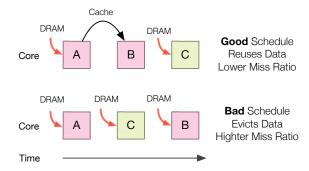

Our GPU database becomes as fast as the CPU version when the tables count a minimum of 800 records with GPU1 and 600 records with GPU2. We obtain relevant speedups on large datasets, and even modest GPUs like our GPU1 are able to procure substantial speedups. Our measures also show that performances of our system are clearly memory bounded and depending of query types, the processing time can be more impacted by the memory bandwidth than by the computation power of GPUs.

These results are encouraging but they are produced on non-indexed tables. When the record number of one table increases, performance of a indexed search in O(log(n)), running on a single thread CPU, overtakes

a trivial parallel brute-force implementation O(n/p), where p is the number of cores. Therefore, we are also currently working on indexation mechanisms for CuDB with better complexity.

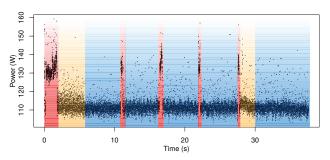

During the performance evaluations, we also measured the total power consumption of our platforms. From the measured values we subtracted the idle power consumption to only show the part of energy consumption involved by the computation of the database system. Figure 3 shows the resulting total consumed energy.

Figure 3: Average energy consumption with JOIN queries.

With our energy consumption tests, we show that the small GPU1 (manufactured in 28 nm) is more efficient than GPU2 (also 28 nm) because of its better "memory bandwidth" over "number of computation units" ratio, what confirms that our GPU database is memory bounded. With CuDB, we are currently working on different types of storage engines with different levels of data compactness and data types. We are also working with SoC architectures to provide a CuDB(m) version which will be dedicated to mobile and embedded applications. Instead of large systems, where the major manufacturers challenge was mainly focused on the processing speed over energy efficiency, small systems dedicated to embedded applications have major energy constraints, particularly due to the portable nature of devices (smartphone, auricular devices). In this field, SoC now offer higher energy efficiency than large systems, mainly due to better integration between components on the same chip (shared memory between CPU and GPU units). So, these small systems using less energy and boosted by environmental constraints, could offer a valuable alternative to existing HPC facilities.

#### IV. Conclusion and Future Works

In this paper, we have introduced CuDB, a GPU boosted relational database engine. CuDB is based on SQLite and preserves its user interface. We measured relevant speedups while the energy efficiency was increased up to 54 times with large datasets. With join queries, our GPU database always outperforms SQLite when tables counted more than one thousand records. Some significant SQL clauses like ORDER BY are still not being supported by our engine. The SQL support of CuDB needs to be improved, as aiming to run full database benchmarks. We need to deal with the GPU memory limitations and we plan to make a hybrid version of our engine where the CPU cores will process queries on small datasets, while the GPU still manages the greediest processing. We also showed that a GPU-boosted database engine is a memory bounded application. The future GPU architectures with stacked memory will drastically improve the available memory bandwidths. NVidia speaks about 1 TB/s with its next Pascal GPU architecture which will still increase the performances of GPU-database engines.

#### Acknowledgment

The authors would like to acknowledge the contribution of the Nesus COST Action IC1305.

#### REFERENCES

- [1] N.K. Govindaraju, B. Lloyd, W. Wang, M. Lin, and D. Manochad, "Fast computation of database operations using graphics processors," in *Proceedings of the 2004 ACM SIGMOD international conference on Management of data*, Paris, France, June 2004, pp. 215-216.

- [2] R. Fang, B. He, M. Lu, K. Yang, N.K. Govindaraju, Q. Luo, and P.V. Sander, "GPUQP: query co-processing using graphics processors," in *Proceedings of the 2007 ACM SIGMOD international conference on Management of data*, Beijing, China, June 2007, pp. 1061-1063.

- [3] P. Bakkum and K. Skadronr, "Accelerating SQL database operations on a GPU with CUDA," in

- Proceedings of the 3rd Workshop on General-Purpose Computation on Graphics Processing, Pittsburgh, Pennsylvania, March 2010, pp. 94-103.

- [4] N. Dechamps, M. Bagein, M. Benjelloun, and S. Mahmoudi, "Boosting Open-Source Database Engines with Graphics Processors," in *Proceedings of the 2012 Seventh International Conference on P2P, Parallel, Grid, Cloud and Internet Computing*, Victoria, Canada, November 2012, pp. 262-266.

- [5] P. Bakkum and S. Chakradhar, "Efficient Data Management for GPU Databases," 2012. http://pbbakkum.com/virginian/paper.pdf Accessed: 2015-08-11.

- [6] B. He, and J. Xu Yu, "High-throughput transaction executions on graphics processors," *VLDB Endowment*, vol. 4, no. 5, pp. 314-325, 2011.

- [7] S. Zhang, J. He, B. He, and M. Lu, "OmniDB: towards portable and efficient query processing on parallel CPU/GPU architectures," *VLDB Endowment*, vol. 6, no. 12, pp. 1374-1377, 2013.

- [8] Y. Yuan, R. Lee, and X. Zhang, "The Yin and Yang of processing data warehousing queries on GPU devices," *VLDB Endowment*, vol. 6, no. 10, pp. 817-828, 2013.

- [9] S. Breß, N. Siegmund, L. Bellatreche, and G. Saake, "An operator-stream-based scheduling engine for effective GPU coprocessing," *Advances in Databases* and *Information Systems*, vol. 8133, pp. 288-301, 2013.

- [10] Parstream, "Parstream turning data into knowledge," White Paper, November 2010.

- [11] GPUdb, www.gpudb.com, Accessed: 2015-07-23.

- [12] T. Mostak, "An overview of MapD (massively parallel database)," White Paper, Massachusetts Institute of Technology, 2013.

- [13] M. Pietron, P. Russek, and K. Wiatr, "Accelerating select where and select join queries on a GPU," *Computer Science (AGH)*, vol. 14, no. 2, pp. 243-252, 2013.

# The analysis of parallel OpenFOAM solver for the heat transfer in electrical power cables

Andrej Bugajev, Raimondas Čiegis

Vilnius Gediminas Technical University, Sauletekio ave. 11, Vilnius andrej.bugajev@vgtu.lt

#### **Abstract**

Here we present the part of results obtained in PhD thesis "The investigation of efficiency of physical phenomena modelling using differential equations on distributed systems" by Andrej Bugajev. This work is dedicated to development of mathematical modelling software. While applying a numerical method it is important to take into account the limited computer resources, the architecture of these resources and how do methods affect software robustness. Three main aspects of this investigation are that software implementation must be efficient, robust and be able to utilize specific hardware resources. The hardware specificity in this work is related to distributed computations. The investigation is done for FVM method usage to implement efficient calculations of a very specific heat transferring problem. That lets to create technological components that make a software implementation robust and efficient. OpenFOAM open source software is selected as a basis for implementation of calculations and a few algorithms to solve efficiency issues are proposed. The FVM parallel solver is implemented and analyzed, it is adapted to heterogeneous cluster Vilkas.

*Keywords* Finite Volume Method, OpenFOAM, parallel algorithms, domain decomposition, distributed computing, parallel computing

#### I. MOTIVATION

This work is dedicated to proposal of technological solutions for developing design rules for power transmission lines and cables (1, [1]), which have to meet the latest power transmission network technical and economical requirements.

In order to do that it is necessary to develop specific software solutions. At present, sizes of the power lines are up to 60% bigger than is necessary in terms of transmitted power. However, as the new distributed generating capacities are installed e.g. large wind farms, bio-gas plants or waist-to-energy plants, the infrastructure of power grid must be re-designed or new optimization strategies for the available grid must be

Figure 1: Typical high-voltage (110 kV) cables [1]

developed. Power cables for power distribution applications are still rated according to IEC 287 and IEC 853 standards, which use the Neher and McGrath meth-

ods proposed in 1957 [2]. Obviously, these formulas cannot accurately account for the various conditions under which the cables are actually installed and used. They estimate the cable's current-carrying capacity (so-called ampacity) with significant margins to stay on the safe side [3]. The safety margins can be quite large and result in 50-70% usage of actual resources. A more accurate mathematical modelling is needed to meet the latest technical and economical requirements and to elaborate new, improved, cost-effective design rules and standards. Today there are many applications where analytical and heuristic formulas cannot describe precisely enough the conditions under which the cables are installed. The present standards require that the cable's current-carrying capacity must be reduced according to the worst-case scenario. To be on the safe side this rule is acceptable, but today the cost effective designing of cable installations comes first as the copper price level has reached its maximum value.

When we need to deal with mathematical models for the heat transfer in various media (metals, insulators, soil, water, air) and non-trivial geometries, only the means of parallel computing technologies can allow us to get results in an adequate time. To solve numerically selected models, we develop our numerical solvers using the OpenFOAM package.

#### II. RELATED WORK

The knowledge of dynamics (in time) of heat distribution in/around electrical cables is necessary to optimize the usage of electricity transferring infrastructure. It is important to determine: maximal electric current for the cable, optimal cable parameters in certain circumstances, cable life expectancy, other engineering factors. To solve the optimization problem it is necessary to implement an efficient modelling software for heat distribution in cables. Fundamentals of the heat distribution in cables are given in [4], but for further readings refer [5, 6, 7]. [8] and [9] presented efficient parallel numerical algorithms for simulation of temperature distribution in electrical cables for mobile devices and cars and solved inverse problem for fitting the diffusion coefficient of the air-isolation material mixture to the experimental data. Numerical algorithms for parabolic and elliptic problems with discontinuous coefficients have been widely investigated in many papers. The use of standard finite element method (FEM) to solve interface problems is equivalent to arithmetic averaging of discontinuous coefficients. The mixed FEM leads to the harmonic averaging if special quadrature formula are used – see, e.g. works by [10] and [5]. Conservative finite-difference schemes for approximation of parabolic and elliptic problems were derived by [11] and [12]. These schemes are robust and use only general assumptions on the position of the interface. Also such finite difference schemes were proposed, which approximate with the second order of accuracy both – the solution and the normal flux through the interface – see [13, 14] for details.

In recent years, scalability and performance of parallel OpenFOAM solvers are actively studied for various applications and HPC platforms. In [15] it is noted that the scalability of parallel OpenFOAM solvers is not very well understood for many applications when executed on massively parallel systems.

We note that an extensive experimental scalability analysis of selected OpenFOAM applications is one of the tasks solved in PRACE (Partnership for Advanced Computing in Europe) project, see [16], [17]. In [16] are presented results on IBM BlueGene/Q (Fermi) and Hewlett Packard C7000 (Lagrange) parallel supercomputers for a few CFD applications with different multiphysics models. The presented experimental results are showing a good scaling and efficiency with up to 2048–4096 cores. It is noted that such results are expected when balancing between computation, message passing and I/O work is good. Obviously, the next generation of ultrascale computing systems will cause additional challenges due to their complexity and heterogeneity.

The most important challenges for parallel solvers implemented in OpenFOAM are the following: a) efficiency of solvers on hybrid heterogeneous parallel systems, b) sensitivity of the parallel preconditioners to data distribution algorithms, c) workload balancing on heterogeneous parallel systems. For mathematical models describing coupled multi-physics problems, it is important to investigate two different approaches to design robust and efficient solvers for such problems [18]. Monolithic solvers operate directly on the

system of nonlinear algebraic equations, obtained after the discretization of the system of PDEs. In the partitioning approache the discrete system is solved by using the single-physics solvers in decoupled fixed-point iterations. The latter aproach is implemented in OpenFOAM. A good review for a comparison of some popular fixed-point methods is given in [19].

#### III. THESIS IDEA

In this work, we study the performance of parallel OpenFOAM-based solver for heat conduction in electrical power cables. For computational experiments, we use the following 2D benchmark problem:

$$\begin{cases} c\rho \frac{\partial T}{\partial t} = \nabla \cdot (\lambda \nabla T) + q, & t \in [0, t_{max}], x \in \Omega, \\ T(x, 0) = T_b, & \text{when } x \in \Omega, \\ T(x, t) = T_b, & \text{when } x \in \partial \Omega, \\ [T] = 0, & [\lambda \nabla T] = 0 & \text{when } x \in \partial \Omega_D, \end{cases}$$

(1)

here  $x=(x_1,x_2)$ , T(x,t) is temperature,  $\lambda(x)>0$  is heat conductivity coefficient, q(x,t,T) is the source function,  $\partial\Omega$  is the contour of domain  $\Omega$ ,  $\rho(x)>0$  defines mass density, c(x)>0 is specific heat capacity,  $T_b$ ,  $t_{max}$  are given constants. Operator  $\nabla\cdot(\lambda\nabla T)=\sum\limits_{j=1}^2\frac{\partial}{\partial x_j}\left(\lambda\frac{\partial T}{\partial x_j}\right)$  is the diffusion operator. The solution and flux continuity conditions are satisfied on boundaries of domains with different diffusion coefficients  $\partial\Omega_D$ .

When we need to deal with 2D and 3D mathematical models for the heat transfer in various media (metals, insulators, soil, water, air) and non-trivial geometries, only parallel computing technologies can allow us to get results in an adequate time. To solve numerically selected models, we develop our numerical solvers using the OpenFOAM package. OpenFOAM is a free, open source CFD software package. It has an extensive set of standard solvers for popular CFD applications. It also allows us to implement new models, numerical schemes and algorithms, utilizing the rich set of OpenFOAM capabilities. The important consequence of this software development approach is that numerical solvers can automatically exploit the basic parallel computing capabilities already available in the OpenFOAM package.

In this work, we study and analyze the parallel performance of OpenFOAM-based solver for heat conduction in electrical power cables. The main goal is to consider the scalability and efficiency of the developed parallel solver in the case when the parallel system is not big, but it consists of non homogeneous multicore nodes. The mesh is adaptive and it is partitioned by using Scotch method. Then load balancing techniques must be used in order to optimize the parallel efficiency of the solver. The second aim is to investigate the sensitivity of parallel preconditioners with respect to the number of processes.

#### IV. Conclusions and future work

- 1. Smaller problems enable a better caching and give a hardware-based speed-up for computations

- 2. The uniform distribution of problems sizes is enough to solve the problem on homogeneous set of nodes, however this strategy is inefficient on heterogeneous set of nodes.

- 3. The load balancing lets to use different nodes efficiently in a heterogeneous cluser.

- 4. The future investigation of parallel efficiency dependence on preconditioners may lead to additional optimization of parallel solvers. This is especially important for large parallel systems.

- 5. One of the main challenges in future work is modelling the problem with multi-physics on parallel systems. In this case some parts of the whole domain have effects, described by Navier-Stokes equations and the rest part has diffusion only.

#### Acknowledgment

The paper was supported by NESUS project "Winter School & PhD Symposium 2016".

#### REFERENCES

[1] Z. Dongping. "Optimierung zwangsgekühlter Energiekabel durch dreidimensionale FEM-

- Simulationen," Doctoral thesis, Universität Duisburg-Essen, 2009.

- [2] J. H. Neher, M. H. McGrath. "The Calculation of the temperature rise and load capability of cable systems," *AIEE Transactions*, Vol. 76, Part III, pp. 752–772, 1957.

- [3] I. Makhkamova. "Numerical Investigations of the Thermal State of Overhead Lines and Underground Cables in Distribution Networks," *Doctoral thesis*, *Durham University*, 2011.

- [4] F. Incropera, P. DeWitt, P. David. *Introduction to heat transfer*, John Willey & Sons, New Yourk, 1985.

- [5] A. Ilgevicius. "Analytical and numerical analysis and simulation of heat transfer in electrical conductors and fuses," *Doctoral thesis, Universität der Bundeswehr München*, 2004.

- [6] A. Ilgevicius, H.D. Liess. "Calculation of the heat transfer in cylindrical wires and electrical fuses by implicit finite volume method," *Mathematical Modelling and Analysis*, Vol. 8, No. 3, pp. 217–228, 2003.

- [7] J. Taler, P. Duda. *Solving Direct and Inverse Heat Conduction Problems*, Springer, Berlin, 2006.

- [8] R. Čiegis, A. Ilgevičius, H. Liess, M. Meilūnas, O. Suboč. "Numerical simulation of the heat conduction in electrical cables," *Mathematical modelling and analysis*, Vol. 12, No. 4, pp. 425–439, 2007.

- [9] Raim. Čiegis, Rem. Čiegis, M. Meilūnas, G. Jankevičiūtė, V. Starikovičius "Parallel numerical algorithm for optimization of electrical cables," *Mathematical modelling and analysis*, Vol. 13, No.4, pp. 471–482, 2008.

- [10] R. Falk, J. Osborn, "Remarks on mixed finite element methods for problems with rough coefficients," *Math. Comp.*, Vol. 62, No. 205, pp. 1–19, 1994.

- [11] A.A. Samarskii, *The Theory of Difference Schemes*. Marcel Dekker, Inc., New York–Basel, 2001.

- [12] A.N. Tichonov, A.A. Samarskii, "Homogeneous finite difference schemes," *Zh. Vychisl. Mat. Mat. Fiziki*, Vol. 1, No. 1, pp. 5–63, 1961.

- [13] V.P. Il'in, "High order accurate finite volumes discretization for Poisson equation," *Siberian Math. J.*, Vol. 37, No.1, pp. 151–169, 1996.

- [14] R. LeVeque, Z. Li. Erratum, "The immersed interface method for elliptic equations with discontinuous coefficients and singular sources," *SIAM J. Numer. Anal.*, Vol. 32, No 5, pp. 1704–1704, 1995.

- [15] O. Rivera, K. Furlinger, D. Kranzimuller, "Investigating the scalability of OpenFOAM for the solution of transport equations and large eddy simulations," *Lecture Notes in Computer Science*, Vol. 7017, pp. 121–130, 2011

- [16] P. Dagna. "OpenFOAM on BG/Q porting and performance," *Prace report*, CINECA, Bologna, Italy 2012.

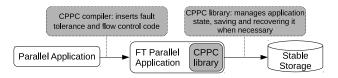

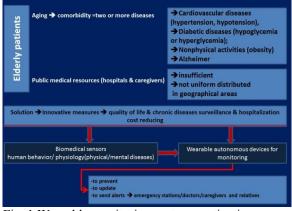

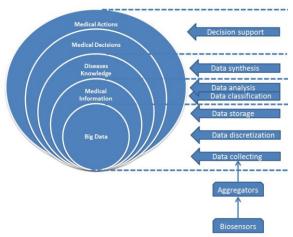

- [17] M. Culpo. "Current bottlenecks in the scalability of OpenFOAM on massively parallel clusters," *Prace white papers*, CINECA, Bologna, Italy 2012.