# Approximate hardening techniques for digital signal processing circuits against radiation-induced faults

by Luis Ángel García Astudillo

A dissertation submitted by in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering, Electronics and Automation

Universidad Carlos III de Madrid

Advisors:

Dr. Luis Entrena Arrontes Dr. Almudena Lindoso Muñoz

Tutor:

Dr. Luis Entrena Arrontes

May 2023

This thesis is distributed under license "Creative Commons Atributtion - Non Commercial - Non Derivatives".

The curse of climbing is discovering how great the distance yet to climb. Steven Erikson

## ACKNOWLEDGEMENTS

Me gustaría empezar esta Tesis con un agradecimiento a todas las personas que la han hecho posible, ayudándome a lo largo de mi etapa educativa e investigadora.

En primer lugar, quiero darles las gracias a mis tutores, el Dr. Luis Entrena y la Dra. Almudena Lindoso, por haberme dado la oportunidad de aprender de ellos. Su apoyo y su guía han sido fundamentales en todos los aspectos de esta Tesis y les estoy profundamente agradecido por haber confiado en mí. También me gustaría darle las gracias a la Dra. Marta Portela, que me introdujo en este apasionante campo durante mi Tesis de Master y me convenció para empezar esta Tesis Doctoral.

Quiero dar las gracias también al resto de profesores y personal administrativo del grupo de Diseño Microelectrónico y Aplicaciones por su apoyo, en especial al Dr. Mario García, cuyo apoyo técnico durante los experimentos ha sido inestimable.

A lo largo de estos años ha pasado mucha gente por el laboratorio en el que he trabajado. A todos ellos quiero agradecerles su compañía y buenos ratos y desearles buena suerte en sus carreras profesionales, a aquellos que ya se fueron, y en sus propias tesis doctorales, a aquellos que, estoy seguro, las acabarán pronto.

A mis padres, mi hermana y a Nerea les quiero agradecer su constante y desinteresado apoyo y cariño todos estos años, sin los cuales no habría llegado hasta aquí. Gracias.

Gracias también a mis amigos, que, aunque la adultez nos ha llevado a pasar menos tiempo juntos, han seguido sacando un rato para tomar algo, tirar unos dados y hablar de libros y música.

Por último, ahora que termino mi etapa como estudiante, que no mi etapa de aprendizaje, me gustaría acordarme de los profesores y profesoras de mis inicios, cuyas enseñanzas me marcaron para ser quien soy, en especial de Chelo, Rosalía, Fermín, Luis y Juan Carlos.

#### PUBLISHED AND SUBMITTED CONTENT

#### First-author published journal articles

[1] L. A. Garcia-Astudillo, L. Entrena, A. Lindoso, *et al.*, "Analyzing Reduced Precision Triple Modular Redundancy under Proton Irradiation," *IEEE Transactions on Nuclear Science*, vol. 69, pp. 470–477, 3 Mar. 2022. doi: 10.1109/TNS.2022.3152088 (JCR Q2). This article has been wholly included in the Thesis in Chapter 3.

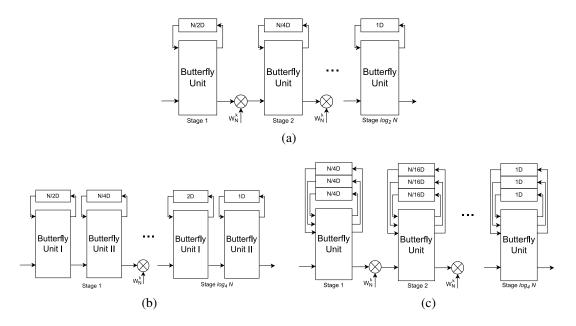

[2] L. Garcia-Astudillo, A. Lindoso, L. Entrena, *et al.*, "Error sensitivity study of FFT architectures implemented in FPGA," *Microelectronics Reliability*, vol. 126, p. 114298, Nov. 2021. doi: 10.1016/J.MICROREL.2021.114298 (JCR Q3). This article has been wholly included in the Thesis in Chapter 4.

[3] L. A. Garcia-Astudillo, A. Lindoso, L. Entrena, *et al.*, "Analyzing Scaled Reduced Precision Redundancy for Error Mitigation under Proton Irradiation," *IEEE Transactions on Nuclear Science*, pp. 1–1, 2022. DOI: 10.1109/TNS.2022.3147599 (JCR Q2). This article has been wholly included in the Thesis in Chapter 5.

[4] L. A. Garcia-Astudillo, L. Entrena, A. Lindoso, *et al.*, "Reduced Resolution Redundancy: A Novel Approximate Error Mitigation Technique," *IEEE Access*, vol. 10, pp. 20643–20651, 2022. doi: 10.1109/ACCESS.2022.3152202 (JCR Q2). This article has been wholly included in the Thesis in Chapter 6.

[5] L. A. Garcia-Astudillo, L. Entrena, A. Lindoso, *et al.*, "Evaluating Reduced Resolution Redundancy for radiation hardening," *IEEE Transactions on Nuclear Science*, 2023, (Early Access). DOI: 10.1109/TNS.2023.3268825 (JCR Q2). This article has been accepted for publication and it is wholly included in the Thesis in Chapter 7.

#### Articles under review

[6] L. A. Garcia-Astudillo, A. Lindoso, and L. Entrena, "Error Mitigation using Optimized Redundancy for Composite Algorithms," *IEEE Transactions on Aerospace and Electronic Systems*, 2023 (JCR Q1). The findings presented in this article have been summarized in Chapter 8 of this Thesis.

[7] P. Aviles, L. Garcia-Astudillo, J. Belloch, *et al.*, "Comparative of proton radiation data for 28 nm Zynq-7000 SoC," *RADECS 2022 - European Conference on Radiation*

and its Effects on Components and Systems, 2022.

#### **Conference** articles

[8] L. A. Garcia-Astudillo, A. Lindoso, M. Portela, *et al.*, "Evaluation of a Reduced Precision Redundancy FFT Design," 2020 35th Conference on Design of Circuits and Integrated Systems, DCIS 2020, Nov. 2020. DOI: 10.1109/DCIS51330.2020.9268634.

Whenever material from these sources is included in this Thesis, it is singled out with typographic means and an explicit reference.

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of Universidad Carlos III de Madrid's products or services. Internal or personal use of this material is permitted. If interested in reprinting/republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/ rights\_link.html to learn how to obtain a License from RightsLink. If applicable, University Microfilms and/or ProQuest Library, or the Archives of Canada may supply single copies of the dissertation.

## **OTHER RESEARCH MERITS**

During the course of this Thesis, the following research merits were awarded to the PhD candidate:

- RADSAGA and RADECS Association Student Grant to participate in the RADECS 2021 Conference.

- RADECS Association, RADSAGA and R2E Student Grant to participate in the RADECS 2022 Conference.

## **RESUMEN NO TÉCNICO**

Se llama radiación al proceso por el cual una partícula o una onda es capaz de transmitir energía a través del espacio o un medio material. Si la energía transmitida es suficientemente alta, la radiación puede provocar que algunos electrones se desplacen de su posición, en un proceso llamado ionización.

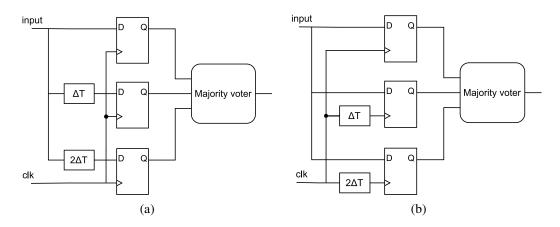

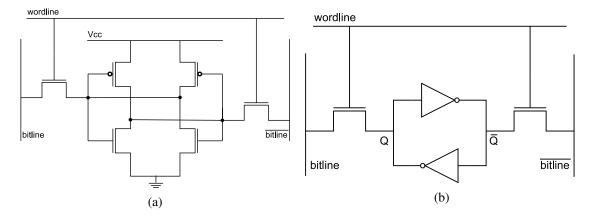

La radiación ionizante puede provocar problemas a los seres vivos, pero también a los diversos materiales que componen los sistemas eléctricos y electrónicos utilizados en entornos sujetos a radiación. Existen en La Tierra varios procesos que emiten radiación ionizante, como la obtención de energía en centrales nucleares o ciertos procedimientos médicos. Sin embargo, las fuentes de radiación más importantes se sitúan más allá de nuestra atmósfera y afectan fundamentalmente a sistemas aeroespaciales y vuelos de gran altitud.

Debido a la radiación, los sistemas electrónicos que se exponen a cualquiera de estas fuentes sufren degradación en sus propiedades a lo largo del tiempo y pueden sufrir fallos catastróficos que acorten su vida útil. El envejecimiento de los componentes se produce por acumulación de carga eléctrica en el material, lo que se conoce como Dosis Ionizante Total (TID por sus siglas en inglés), o por distorsiones en el silicio sobre el que se fabrican los circuitos, lo que se conoce como Daño por Desplazamiento (DD). Una única partícula ionizante puede, sin embargo, provocar también diversos tipos de fallos transitorios o permanentes en los componentes de un circuito, generalmente por un cambio de estado en un elemento de memoria o fallos destructivos en un transistor. Los diferentes tipos de fallos producidos en circuitos por la acción de una única partícula ionizante se engloban en la categoría de Efectos de Evento Único (SEE por sus siglas en inglés).

Para proteger los sistemas electrónicos frente a los efectos de la radiación se suele recurrir a un conjunto de técnicas que llamamos endurecimiento frente a radiación. Los procedimientos tradicionales de endurecimiento han consistido en la fabricación de componentes electrónicos mediante procesos especiales que les confieran una resistencia inherente frente a la TID, el DD y los SEE. A este conjunto de técnicas de endurecimiento se lo conoce como Endurecimiento frente a la Radiación Por Proceso (RHBP por sus siglas en inglés). Estos procedimientos suelen aumentar el coste de los componentes y empeorar su rendimiento con respecto a los componentes que usamos en nuestros sistemas electrónicos cotidianos.

En oposición a las técnicas RHBP encontramos las técnicas de Endurecimiento frente a la Radiación Por Diseño (RHBD por sus siglas en inglés). Estas técnicas permiten detectar y tratar de corregir fallos producidos por la radiación introduciendo modificaciones en los circuitos. Estas modificaciones suelen aumentar la complejidad de los circuitos que se quiere endurecer, haciendo que consuman más energía, ocupen más espacio o funcionen a menor frecuencia, pero estas desventajas se pueden compensar con

la disminución de los costes de fabricación y la mejora en las prestaciones que aportan los sistemas modernos.

En un intento por reducir el coste de las misiones espaciales y mejorar sus capacidades, en los últimos años se trata de introducir un mayor número de Componentes Comerciales (COTS por sus siglas en inglés), endurecidos mediante técnicas RHBD.

Las técnicas RHBD habituales se basan en la adición de elementos redundantes idénticos al original, cuyos resultados se pueden comparar entre sí para obtener información acerca de la existencia de un error (si sólo se usa un circuito redundante, Duplicación Con Comparación [DWC]) o llegar incluso a corregir un error detectado de manera automática, si se emplean dos o más réplicas redundantes, siendo el caso más habitual la Redundancia Modular Triple (TMR) en todas sus variantes.

El trabajo desarrollado en esta Tesis gira en torno a las técnicas de endurecimiento RHBD de sistemas electrónicos comerciales. En concreto, se trata de proponer y caracterizar nuevas técnicas de endurecimiento que permitan reducir el alto consumo de recursos de las utilizadas habitualmente. Para ello, se han desarrollado técnicas de endurecimiento que aprovechan cálculos aproximados para detectar y corregir fallos en circuitos electrónicos digitales para procesamiento de señal implementados en FPGA comerciales, dispositivos que permiten implementar circuitos electrónicos digitales a medida y reconfigurarlos tantas veces como se quiera.

A lo largo de esta Tesis se han desarrollado diferentes circuitos de prueba endurecidos mediante TMR y se ha comparado su rendimiento con los de otras técnicas de Redundancia Aproximada, en concreto la Redundancia de Precisión Reducida (RPR), la Redundancia de Resolución Reducida (RRR) y la Redundancia Optimizada para Algoritmos Compuestos (ORCA):

- La Redundancia de Precisión Reducida se basa en la utilización de dos réplicas redundantes que calculan resultados con un menor número de bits que el circuito original. De este modo se pueden disminuir los recursos necesitados por el circuito, aunque las correcciones en caso de fallo son menos precisas que en el TMR. En este trabajo exploramos también la RPR Escalada como un método de obtener un balance óptimo entre la precisión y el consumo de recursos.

- La Redundancia de Resolución Reducida es una técnica propuesta originalmente en esta tesis. Está pensada para algoritmos que trabajan con información en forma de paquetes cuyos datos individuales guardan alguna relación entre sí. Las réplicas redundantes calculan los resultados con una fracción de los datos de entrada originales, lo que reduce su tamaño y permite correcciones aproximadas en caso de fallo.

- La Redundancia Optimizada para Algoritmos Compuestos es también una aportación original de esta tesis. Está indicada para algoritmos cuyo resultado final puede expresarse como la composición de resultados intermedios calculados en etapas anteriores. Las réplicas redundantes se forman como bloques que calculan resultados

intermedios y el resultado de su composición se puede comparar con el resultado original. Este método permite reducir recursos y proporciona resultados de corrección exactos en la mayor parte de los casos, lo que supone una mejora importante con respecto a las correcciones de los métodos anteriores.

La eficacia de las técnicas de endurecimiento desarrolladas se ha probado mediante experimentos de inyección de fallos y mediante ensayos en instalaciones de aceleradores de partículas preparadas para la irradiación de dispositivos electrónicos. En concreto, se han realizado ensayos de radiación con protones en el Centro Nacional de Aceleradores (CNA España), el Paul Scherrer Institut (PSI, Suiza) y ensayos de radiación con neutrones en el laboratorio ISIS Neutron and Muon Source (ChipIR, Reino Unido).

## NON-TECHNICAL SUMMARY

Radiation is the process by which a particle or wave is able to transmit energy through space or a material medium. If the energy transmitted is high enough, radiation can cause some electrons to move out of position, in a process called ionization.

Ionizing radiation can cause problems for living beings, but also for the various materials that make up electrical and electronic systems used in environments subject to radiation. There are several processes on Earth that emit ionizing radiation, such as obtaining energy in nuclear power plants or certain medical procedures. However, the most important sources of radiation are located beyond our atmosphere and mainly affect aerospace systems and high-altitude flights.

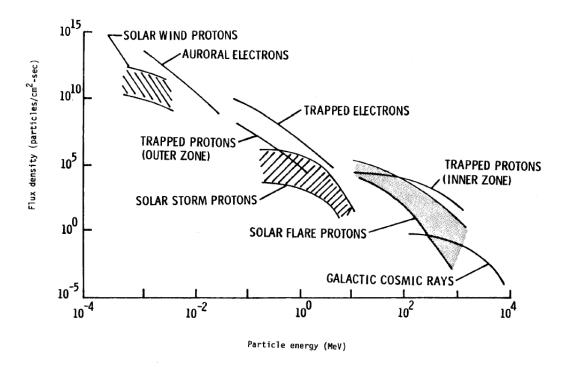

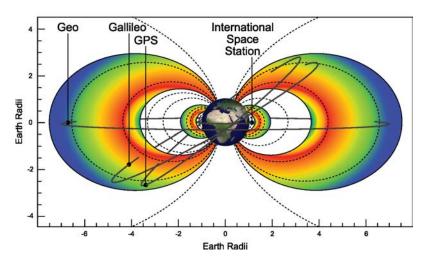

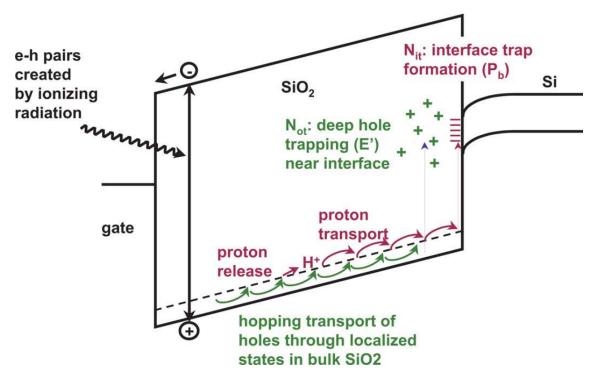

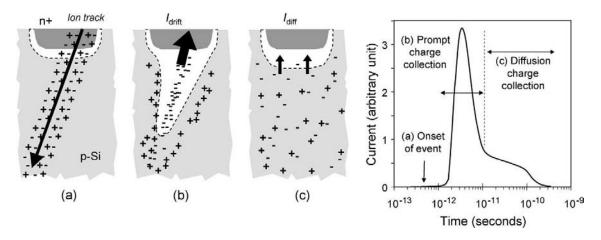

Due to radiation, electronic systems exposed to any of these sources suffer degradation in their properties over time and can suffer catastrophic failures that shorten their useful life. Component aging is caused by accumulation of electrical charge in the material, known as Total Ionizing Dose (TID), or by distortions in the silicon on which the circuits are fabricated, known as Displacement Damage (DD). A single ionizing particle can, however, also cause various types of transient or permanent failures in the components of a circuit, usually by a change of state in a memory element or destructive failures in a transistor. The different types of failures produced in circuits by the action of a single ionizing particle fall into the category of Single Event Effects (SEE).

To protect electronic systems against the effects of radiation, a set of techniques known as radiation hardening is commonly used. Traditional hardening procedures have consisted of manufacturing electronic components using special processes that give them inherent resistance to TID, DD and SEE. This set of hardening techniques is known as Radiation Hardening By Process (RHBP). These procedures tend to increase the cost of components and worsen their performance relative to the components we use in our everyday electronic systems.

Opposed to RHBP techniques we find Radiation Hardening By Design (RHBD) techniques. These techniques allow us to detect faults and attempt to correct them by inserting modifications in the circuit. These modifications typically increase the complexity of the circuits to be hardened, causing them to consume more power, use more area or operate at lower frequencies, but these disadvantages can be compensated by the lower costs and improved performance provided by modern systems.

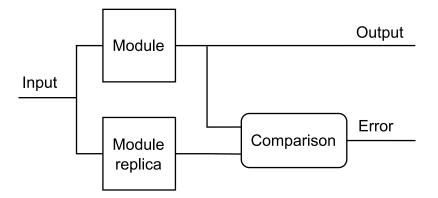

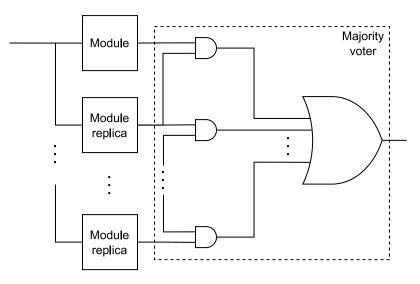

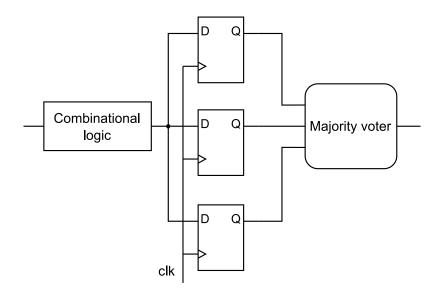

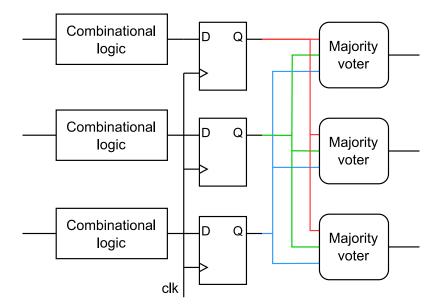

In an attempt to reduce the cost of space missions and improve their capabilities, efforts have been made in recent years to introduce more Commercial Off-The-Shelf (COTS) components, hardened with RHBD approaches. The usual RHBD techniques are based on the addition of redundant elements identical to the original, whose results can be compared with each other to obtain information about the existence of an error

(if only one redundant circuit is used, Duplication With Comparison [DWC]) or even correct an error detected automatically, if two or more redundant replicas are used, the most common case being Triple Modular Redundancy (TMR) in all its variants.

The work developed in this Thesis revolves around RHBD hardening techniques for commercial electronic systems. Specifically, the aim is to propose and characterize new hardening techniques to reduce the high resource consumption of those commonly used. For this purpose, we have developed hardening techniques that take advantage of approximate calculations to detect and correct faults in digital electronic circuits for signal processing implemented in commercial FPGA, devices that allow to implement custom digital electronic circuits and reconfigure them as many times as desired.

Throughout this Thesis, different TMR-hardened test circuits have been developed and their performance has been compared with those of other Approximate Redundancy techniques, namely Reduced Precision Redundancy (RPR), Reduced Resolution Redundancy (RRR) and Optimized Redundancy for Composite Algorithms (ORCA):

- Reduced Precision Redundancy is based on the use of two redundant replicas that compute results with a smaller number of bits than the original circuit. In this way, the resources needed by the circuit can be decreased, although the corrections in case of failure are less accurate than in TMR. In this paper we also explore Scaled RPR as a method of obtaining an optimal balance between accuracy and resource consumption.

- Reduced Resolution Redundancy is a technique originally proposed in this thesis. It is intended for algorithms that work with information in the form of packets whose individual data have some relationship with each other. Redundant replicas compute results with a fraction of the original input data, which reduces their size and allows approximate corrections in case of failure.

- Optimized Redundancy for Composite Algorithms is also an original contribution of this thesis. It is suitable for algorithms whose final result can be expressed as the composition of intermediate results computed in previous stages. Redundant replicas are formed as blocks that compute intermediate results and the result of their composition can be compared with the original result. This method reduces resources and provides accurate correction results in most cases, which is a significant improvement over the corrections of previous methods.

The effectiveness of the developed hardening techniques has been tested by fault injection experiments and by testing in particle accelerator facilities prepared for irradiation of electronic devices. In particular, proton irradiation campaigns have been carried out at Centro Nacional de Aceleradores (CNA, Spain) and at Paul Scherrer Institut (PSI, Switzerland), and neutron irradiation campaigns have been performed at the ISIS Neutron and Muon Source laboratory (ChipIR, United Kingdom).

## **RESUMEN TÉCNICO**

Se llama radiación al proceso por el cual una partícula o una onda es capaz de transmitir energía a través del espacio o un medio material. Si la energía transmitida es suficientemente alta, la radiación puede provocar que algunos electrones se desplacen de su posición, en un proceso llamado ionización.

La radiación ionizante puede provocar problemas a los seres vivos, pero también a los diversos materiales que componen los sistemas eléctricos y electrónicos utilizados en entornos sujetos a radiación. Existen en La Tierra varios procesos que emiten radiación ionizante, como la obtención de energía en centrales nucleares o ciertos procedimientos médicos. Sin embargo, las fuentes de radiación más importantes se sitúan más allá de nuestra atmósfera y afectan fundamentalmente a sistemas aeroespaciales y vuelos de gran altitud.

Debido a la radiación, los sistemas electrónicos que se exponen a cualquiera de estas fuentes sufren degradación en sus propiedades a lo largo del tiempo y pueden sufrir fallos catastróficos que acorten su vida útil. El envejecimiento de los componentes se produce por acumulación de carga eléctrica en el material, lo que se conoce como Dosis Ionizante Total (TID, Total Ionizing Dose), o por distorsiones acumuladas en la matriz cristalina del silicio en el que se fabrican los circuitos, lo que se conoce como Daño por Desplazamiento (DD, Displacement Damage). Una única partícula ionizante puede, sin embargo, provocar también diversos tipos de fallos transitorios o permanentes en los componentes de un circuito, generalmente por un cambio de estado en un elemento de memoria o la activación de circuitos parasitarios en un transistor. Los diferentes tipos de fallos producidos en circuitos por la acción de una única partícula ionizante se engloban en la categoría de Efectos de Evento Único (SEE, Single Event Effects).

Para proteger los sistemas electrónicos frente a los efectos de la radiación se suele recurrir a un conjunto de técnicas que llamamos endurecimiento frente a radiación. Los procedimientos tradicionales de endurecimiento han consistido en la fabricación de componentes electrónicos mediante procesos especiales que les confieran una resistencia inherente frente a la TID, el DD y los SEE. A este conjunto de técnicas de endurecimiento se lo conoce como Endurecimiento frente a la Radiación Por Proceso (RHBP, por sus siglas en inglés). Estos procedimientos suelen aumentar el coste de los componentes y empeorar su rendimiento con respecto a los componentes que usamos en nuestros sistemas electrónicos cotidianos.

En oposición a las técnicas RHBP encontramos las técnicas de Endurecimiento frente a la Radiación Por Diseño (RHBD, por sus siglas en inglés). Estas técnicas permiten detectar y tratar de corregir fallos producidos por la radiación introduciendo modificaciones en los circuitos. Estas modificaciones suelen aumentar la complejidad de los circuitos que se quiere endurecer, haciendo que consuman más energía, ocupen más

espacio o funcionen a menor frecuencia, pero estas desventajas se pueden compensar con la disminución de los costes de fabricación y la mejora en las prestaciones que aportan los sistemas modernos.

En un intento por reducir el coste de las misiones espaciales y mejorar sus capacidades, en los últimos años se trata de introducir un mayor número de Componentes Comerciales (COTS, por sus siglas en inglés), endurecidos mediante técnicas RHBD.

Las técnicas RHBD habituales se basan en la adición de elementos redundantes idénticos al original, cuyos resultados se pueden comparar entre sí para obtener información acerca de la existencia de un error (si sólo se usa un circuito redundante, Duplicación Con Comparación [DWC, Duplication With Comparison]) o llegar incluso a corregir un error detectado de manera automática, si se emplean dos o más réplicas redundantes, siendo el caso más habitual la Redundancia Modular Triple (TMR, Triple Modular Redundancy) en todas sus variantes.

El trabajo desarrollado en esta Tesis gira en torno a las técnicas de endurecimiento RHBD de sistemas electrónicos comerciales. En concreto, se trata de proponer y caracterizar nuevas técnicas de endurecimiento que permitan reducir el alto consumo de recursos de las técnicas utilizadas habitualmente. Para ello, se han desarrollado técnicas de endurecimiento que aprovechan cálculos aproximados para detectar y corregir fallos en circuitos electrónicos digitales para procesamiento de señal implementados en FPGA (Field Programmable Gate Array) comerciales.

Las FPGA son dispositivos que permiten implementar circuitos electrónicos digitales diseñados a medida y reconfigurarlos tantas veces como se quiera. Su capacidad de reconfiguración y sus altas prestaciones las convierten en dispositivos muy interesantes para aplicaciones espaciales, donde realizar cambios en los diseños no suele ser posible una vez comenzada la misión. La reconfigurabilidad de las FPGA permite corregir en remoto posibles problemas en el diseño, pero también añadir o modificar funcionalidades a los circuitos implementados en el sistema.

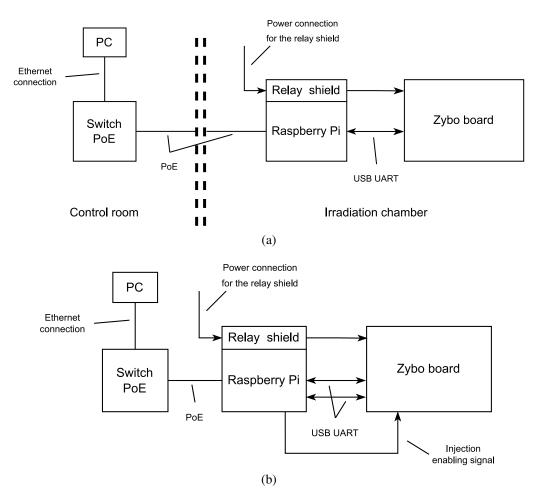

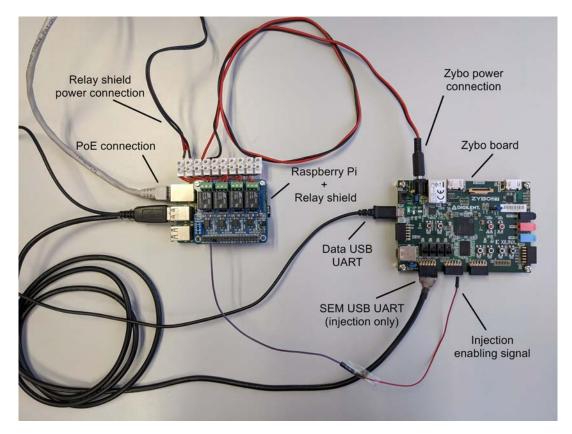

La eficacia de las técnicas de endurecimiento desarrolladas e implementadas en FPGAs se ha probado mediante experimentos de inyección de fallos y mediante ensayos en instalaciones de aceleradores de partículas preparadas para la irradiación de dispositivos electrónicos.

Los ensayos de radiación son el estándar industrial para probar el comportamiento de todos los sistemas electrónicos que se envían a una misión espacial. Con estos ensayos se trata de emular de manera acelerada las condiciones de radiación a las que se verán sometidos los sistemas una vez hayan sido lanzados y determinar su resistencia a TID, DD y/o SEEs. Dependiendo del efecto que se quiera observar, las partículas elegidas para la radiación varían, pudiendo elegirse entre electrones, neutrones, protones, iones pesados, fotones... Particularmente, los ensayos de radiación realizados en este trabajo, tratándose de un estudio de técnicas de endurecimiento para sistemas electrónicos digitales, están destinados a establecer la sensibilidad de los circuitos estudiados frente a un tipo de SEE

conocido como Single Event Upset (SEU), en el que la radiación modifica el valor lógico de un elemento de memoria. Para ello, hemos recurrido a experimentos de radiación con protones en el Centro Nacional de Aceleradores (CNA, España), el Paul Scherrer Institut (PSI, Suiza) y experimentos de radiación con neutrones en el laboratorio ISIS Neutron and Muon Source (ChipIR, Reino Unido).

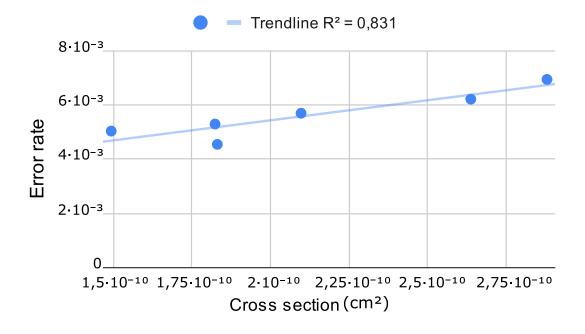

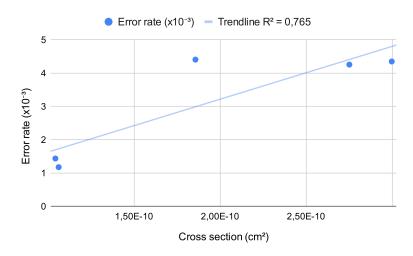

La sensibilidad de un circuito suele medirse en términos de su sección eficaz (*cross section*) con respecto a una partícula determinada, calculada como el cociente entre el número de fallos encontrados y el número de partículas ionizantes por unidad de área utilizadas en la campaña de radiación. Esta métrica sirve para estimar el número de fallos que provocará la radiación a lo largo de la vida útil del sistema, pero también para establecer comparaciones que permitan conocer la eficacia de los sistemas de endurecimiento implementados y ayudar a mejorarlos.

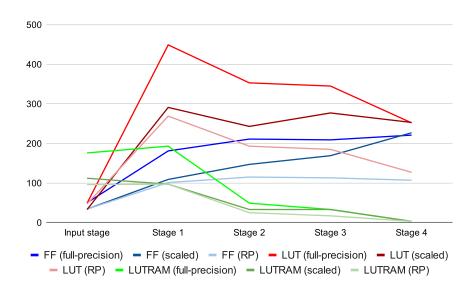

El método de inyección de fallos utilizado en esta Tesis como complemento a la radiación se basa en modificar el valor lógico de los datos almacenados en la memoria de configuración de la FPGA. En esta memoria se guarda la descripción del funcionamiento del circuito implementado en la FPGA, por lo que modificar sus valores equivale a modificar el circuito. En FPGAs que utilizan la tecnología SRAM en sus memorias de configuración, como las utilizadas en esta Tesis, este es el componente más sensible a la radiación, por lo que es posible comparar los resultados de la inyección de fallos y de las campañas de radiación. Análogamente a la sección eficaz, en experimentos de inyección de fallos podemos hablar de la tasa de error, calculada como el cociente entre el número de fallos encontrados y la cantidad de bits de memoria inyectados.

A lo largo de esta Tesis se han desarrollado diferentes circuitos endurecidos mediante Redundancia Modular Triple y se ha comparado su rendimiento con los de otras técnicas de Redundancia Aproximada, en concreto la Redundancia de Precisión Reducida (RPR), la Redundancia de Resolución Reducida (RRR) y la Redundancia Optimizada para Algoritmos Compuestos (ORCA). Estas dos últimas son contribuciones originales presentadas en esta Tesis.

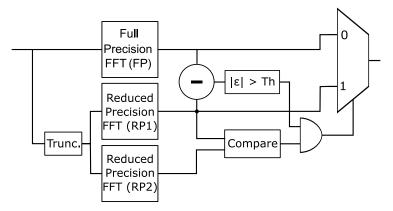

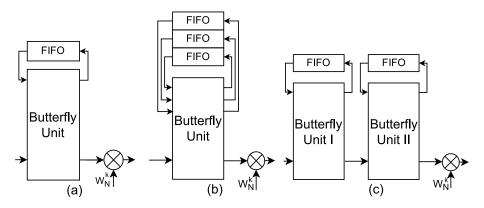

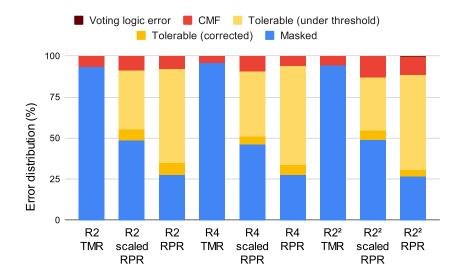

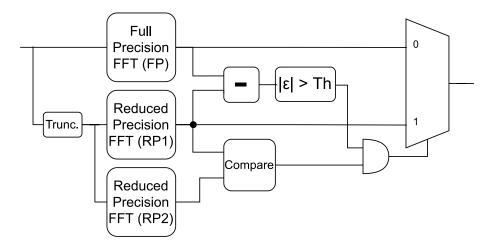

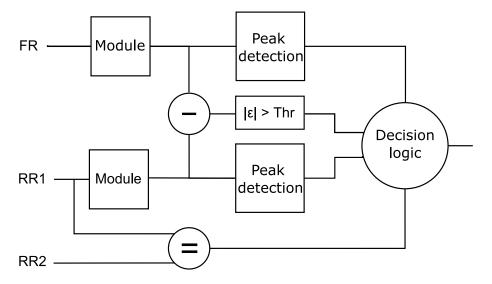

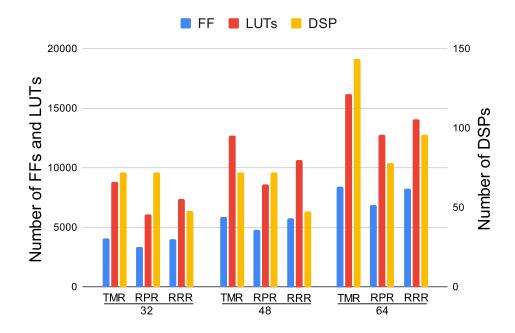

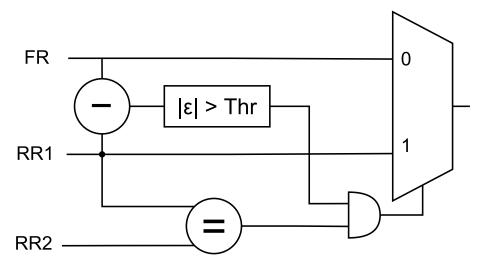

• La Redundancia de Precisión Reducida se basa en la utilización de dos réplicas redundantes que calculan resultados con un menor número de bits que el circuito original. Para cada dato de salida se comparan el resultado del circuito original y los dos resultados de precisión reducida. Si los dos resultados de precisión reducida son idénticos y su diferencia con el resultado de precisión completa es mayor que un determinado valor umbral, se considera que existe un fallo en el circuito original y se utiliza el resultado de precisión reducida para corregirlo. En cualquier otro caso, el resultado original se considera correcto, aunque pueda contener errores tolerables por debajo del umbral de comparación. En comparación con un circuito endurecido con TMR, los diseños RPR utilizan menos recursos, debido a la reducción en la precisión de los cálculos de los circuitos redundantes. No obstante, esto también afecta a la calidad de los resultados obtenidos cuando se corrige un error.

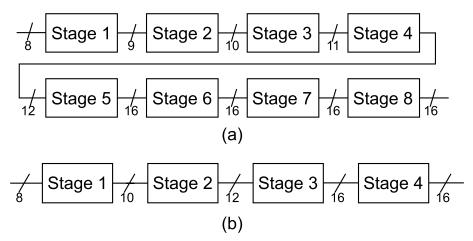

En este trabajo exploramos también la RPR Escalada como un método de obtener un balance óptimo entre la precisión y el consumo de recursos. En esta variante de la técnica RPR, los resultados de cada etapa de cálculo en los circuitos redundantes tienen una precisión diferente, incrementándose hacia las últimas etapas, en las que el resultado tiene la misma precisión que el circuito original. Con este método se logra incrementar la calidad de los datos corregidos a la vez que se reducen los recursos utilizados por el endurecimiento.

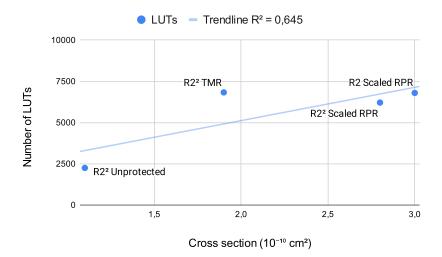

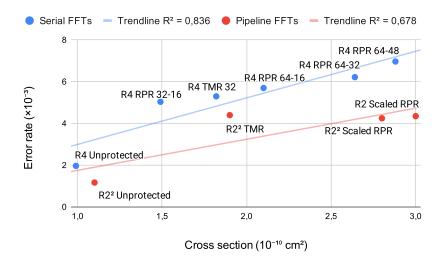

Los resultados de las campañas de radiación y de inyección de fallos realizadas sobre los diseños endurecidos con RPR sugieren que la reducción de recursos no sólo es beneficiosa por sí misma en términos de recursos y energía utilizados por el sistema, sino que también conlleva una reducción de la sensibilidad de los circuitos, medida tanto en cross section como en tasa de error.

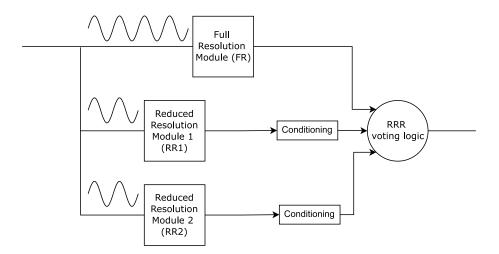

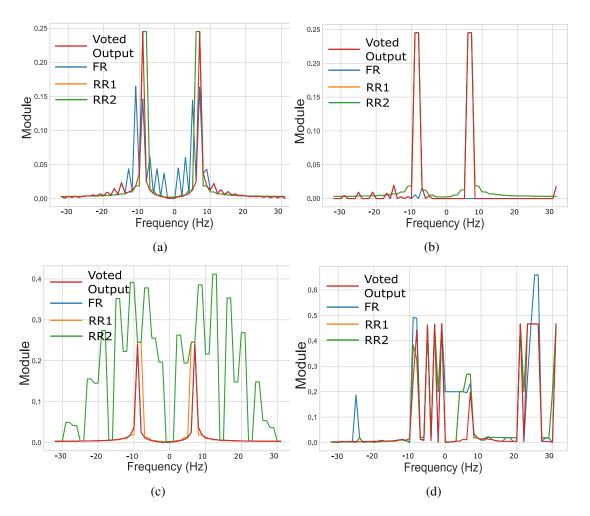

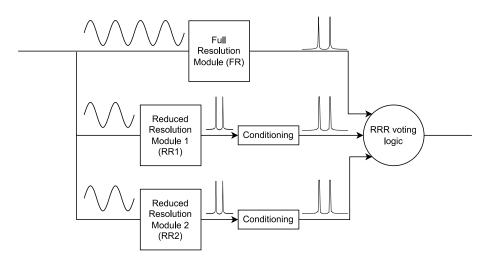

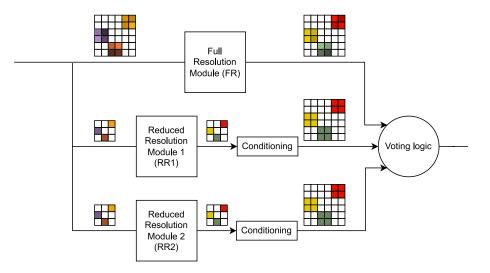

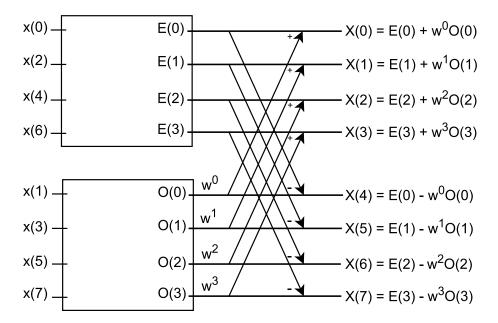

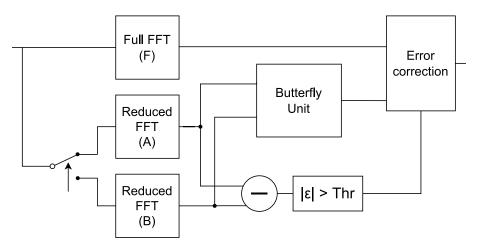

• La Redundancia de Resolución Reducida es una técnica propuesta originalmente en esta tesis. Está indicada para algoritmos que trabajan con información en forma de paquetes cuyos datos individuales guardan alguna relación entre sí, como puede ser un algoritmo de procesamiento de imágenes. En la técnica RRR, se añaden dos circuitos redundantes que calculan los resultados con una fracción de los datos de entrada originales. Tras el cálculo, los resultados diezmados pueden interpolarse para obtener un resultado aproximado del mismo tamaño que el resultado del circuito original. Una vez interpolados, los resultados de los tres circuitos pueden ser comparados para detectar y corregir fallos de una manera similar a la que se utiliza en la técnica RPR. Aprovechando las características del diseño hardware, la disminución de la cantidad de datos que procesan los circuitos de Resolución Reducida puede traducirse en una disminución de recursos, en lugar de una disminución de tiempo de cálculo. De esta manera, la técnica RRR es capaz de reducir el consumo de recursos en comparación a los que se necesitarían si se utilizase un endurecimiento TMR.

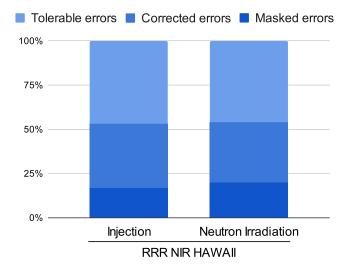

Los resultados de los experimentos realizados en diseños endurecidos mediante Redundancia de Resolución Reducida sugieren que la técnica es eficaz en reducir los recursos utilizados y, al igual que pasaba en el caso de la Redundancia de Precisión Reducida, también su sensibilidad se ve reducida, comparada con la sensibilidad del mismo circuito endurecido con Redundancia Modular Triple. Además, se observa una reducción notable de la sensibilidad de los circuitos frente a errores no corregibles, comparado con el mismo resultado en TMR y RPR. Este tipo de error engloba aquellos producidos por fallos en la lógica de comparación y votación o aquellos en los que un único SEU produce fallos en los resultados de dos o más de los circuitos redundantes al mismo tiempo, lo que se conoce como Fallo en Modo Común (CMF). No obstante, también se observa que la calidad de las correcciones realizadas utilizando este método empeora ligeramente.

• La Redundancia Optimizada para Algoritmos Compuestos es también una aportación original de esta tesis. Está indicada para algoritmos cuyo resultado final puede

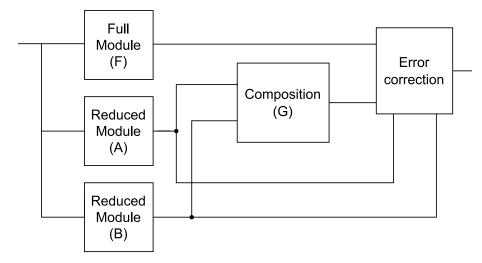

expresarse como la composición de resultados intermedios calculados en etapas anteriores. Para endurecer un circuito usando esta técnica, se añaden dos circuitos redundantes diferentes entre sí y que procesan cada uno una parte diferente del conjunto de datos de entrada. Cada uno de estos circuitos aproximados calcula un resultado intermedio. La composición de los dos resultados intermedios da un resultado idéntico al del circuito original en ausencia de fallos.

La detección de fallos se realiza comparando el resultado del circuito original con el de la composición de los circuitos aproximados. En caso de ser diferentes, se puede determinar el origen del fallo comparando los resultados aproximados intermedios frente a un umbral. Si la diferencia entre los resultados intermedios supera el umbral, significa que el fallo se ha producido en uno de los circuitos aproximados y que el resultado de la composición no debe ser utilizado en la salida. Al igual que ocurre en la Redundancia de Precisión Reducida y la Redundancia de Resolución Reducida, utilizar un umbral de comparación implica la existencia de errores tolerables. No obstante, esta técnica de endurecimiento permite realizar correcciones exactas, en lugar de aproximadas, en la mayor parte de los casos, lo que mejora la calidad de los resultados con respecto a otras técnicas de endurecimiento aproximadas, al tiempo que reduce los recursos utilizados por el sistema endurecido en comparación con las técnicas tradicionales.

Los resultados de los experimentos realizados con diseños endurecidos mediante Redundancia Optimizada para Algoritmos Compuestos confirman que esta técnica de endurecimiento es capaz de producir correcciones exactas en un alto porcentaje de los eventos. Su sensibilidad frente a todo tipo de errores y frente a errores no corregibles también se ve disminuida, comparada con la obtenida con Redundancia Modular Triple.

Los resultados presentados en esta Tesis respaldan la idea de que las técnicas de Redundancia Aproximada son alternativas viables a las técnicas de endurecimiento frente a la radiación habituales, siempre que las características del sistema toleren la presencia de resultados no exactos. La Redundancia Aproximada logra reducir el área y el consumo de recursos de los circuitos endurecidos a costa de realizar correcciones aproximadas, que van desde obtener menor precisión en los resultados corregidos (RPR), correcciones basadas en resultados correctos próximos (RRR) o correcciones exactas en algunos casos y de menor precisión en otros (ORCA). En cualquiera de los casos, estas correcciones aproximadas pueden ser percibidas como mero ruido por el sistema y no afectar a su funcionalidad.

Las campañas de radiación y de inyección de fallos muestran que las técnicas de Endurecimiento Aproximado reducen la sensibilidad de los circuitos endurecidos (con respecto a la del mismo circuito endurecido con Redundancia Modular Triple) como consecuencia de la reducción de recursos. Comparar los resultados de ambos tipos de campañas nos ha permitido establecer una relación entre ellas, lo que valida el método de inyección de fallos y lo sitúa como una manera rápida y económica de obtener resultados preliminares. La inyección de fallos nos ha permitido, por un lado, depurar el funcionamiento de las técnicas propuestas sin necesidad de someterlas a ensayos de radiación o largas campañas de simulación, y por otro, conocer de antemano la sensibilidad y capacidad de corrección de errores de las técnicas de endurecimiento propuestas. Estas dos ventajas nos han permitido realizar una planificación de las campañas de radiación más adecuada, aprovechando al máximo el tiempo de radiación disponible y minimizando los costes de los experimentos.

Además de estas características, los resultados obtenidos sugieren que la manera en que las técnicas de Redundancia de Resolución Reducida y en la Redundancia Optimizada para Algoritmos Compuestos tratan los datos reduce la incidencia de Fallos en Modo Común, que son responsables de gran parte de los fallos no corregibles en todos los sistemas endurecidos mediante técnicas RHBD.

## **TECHNICAL SUMMARY**

Radiation is the process by which a particle or wave is able to transmit energy through space or a material medium. If the energy transmitted is high enough, radiation can cause some electrons to move out of position, in a process called ionization.

Ionizing radiation can cause problems for living beings, but also for the various materials that make up electrical and electronic systems used in environments subject to radiation. There are several processes on Earth that emit ionizing radiation, such as obtaining energy in nuclear power plants or certain medical procedures. However, the most important sources of radiation are located beyond our atmosphere and mainly affect aerospace systems and high-altitude flights.

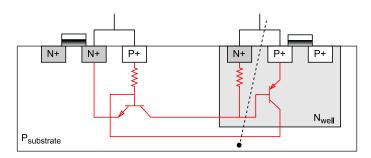

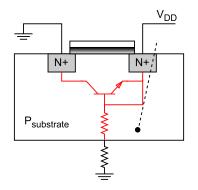

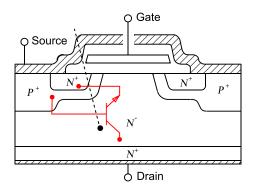

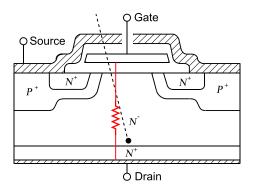

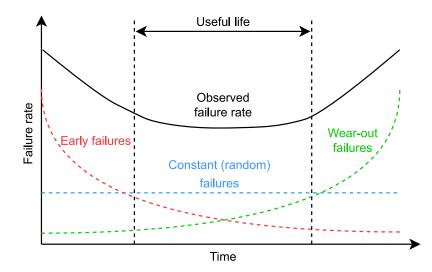

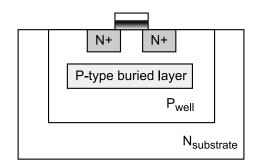

Due to radiation, electronic systems exposed to any of these sources suffer degradation in their properties over time and can suffer catastrophic failures that shorten their useful life. Component aging is caused by accumulation of electrical charge in the material, known as Total Ionizing Dose (TID), or by accumulated distortions in the crystalline matrix of the silicon in which the circuits are made, known as Displacement Damage (DD). A single ionizing particle can, however, also cause various types of transient or permanent failures in the components of a circuit, usually by a change of state in a memory element or the activation of parasitic circuits in a transistor. The different types of faults produced in circuits by the action of a single ionizing particle fall into the category of Single Event Effects (SEE).

To protect electronic systems against the effects of radiation, a set of techniques known as radiation hardening is often used. Traditional hardening procedures have consisted of manufacturing electronic components using special processes that give them inherent resistance to TID, DD and SEE. This set of hardening techniques is known as Radiation Hardening By Process (RHBP). These procedures tend to increase the cost of components and worsen their performance relative to the components we use in our everyday electronic systems.

In opposition to RHBP techniques we find Radiation Hardening by Design (RHBD) techniques. These techniques allow us to detect and attempt to correct radiation induced failures by introducing modifications to the circuits. These modifications often increase the complexity of the circuits to be hardened, causing them to consume more power, take up more space or operate at a lower frequency. However, these disadvantages can be offset by the reduced manufacturing costs and improved performance provided by modern systems.

In an attempt to reduce the cost of space missions and improve their capabilities, efforts have been made in recent years to introduce more Commercial Off-The-Shelf (COTS) components, hardened with RHBD approaches.

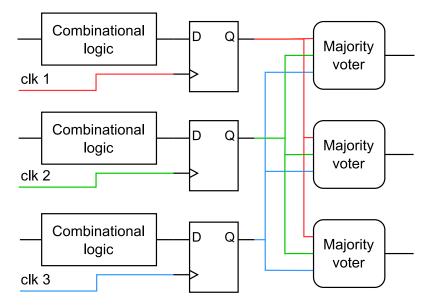

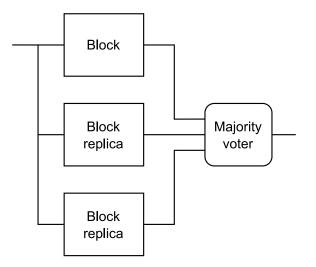

The usual RHBD techniques are based on the addition of redundant elements identical to the original, whose results can be compared with each other to obtain information about the existence of an error (if only one redundant circuit is used, Duplication With Comparison [DWC]) or even to correct an error detected automatically, if two or more redundant replicas are used, the most common case being Triple Modular Redundancy (TMR) in all its variants.

The work developed in this Thesis revolves around RHBD hardening techniques for commercial electronic systems. Specifically, the aim is to propose and characterize new hardening techniques to reduce the high resource consumption of commonly used techniques. To this end, we have developed hardening techniques that take advantage of approximate calculations to detect and correct faults in digital electronic circuits for signal processing implemented in commercial FPGAs (Field Programmable Gate Array).

FPGAs are devices that allow custom-designed digital electronic circuits to be implemented and reconfigured as many times as desired. Their reconfigurability and high performance make them very interesting devices for space applications, where design changes are usually not possible once the mission has started. The reconfigurability of FPGAs allows to remotely correct possible problems in the design, but also to add or modify functionalities to the circuits implemented in the system.

The effectiveness of the hardening techniques developed and implemented in FPGAs has been proven by fault injection experiments and by testing in particle accelerator facilities prepared for irradiation of electronic devices.

Irradiation tests are the industry standard for testing the behavior of all electronic systems that are sent on a space mission. The purpose of these tests is to emulate in an accelerated manner the radiation conditions to which the systems will be subjected once they have been launched and to determine their resistance to TID, DD and/or SEEs. Depending on the effects to be observed, the particles chosen for the radiation vary, being able to choose between electrons, neutrons, protons, heavy ions, photons... In particular, the radiation tests carried out in this work, being a study of hardening techniques for digital electronic systems, are aimed at establishing the sensitivity of the circuits studied against a type of SEE known as Single Event Upset (SEU), in which radiation modifies the logic value of a memory element. For this purpose, we have used radiation experiments with protons at the Centro Nacional de Aceleradores (CNA, Spain), the Paul Scherrer Institut (PSI, Switzerland) and radiation experiments with neutrons at the ISIS Neutron and Muon Source laboratory (ChipIR, UK).

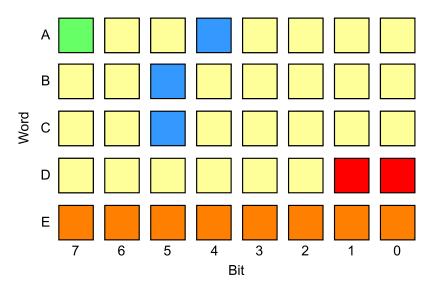

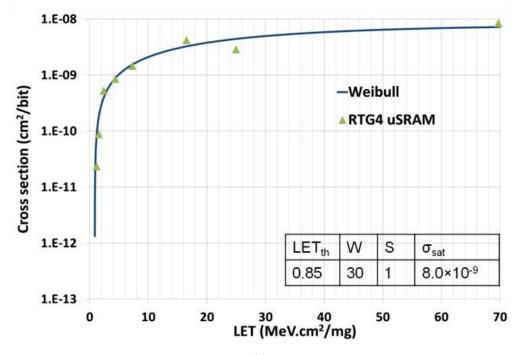

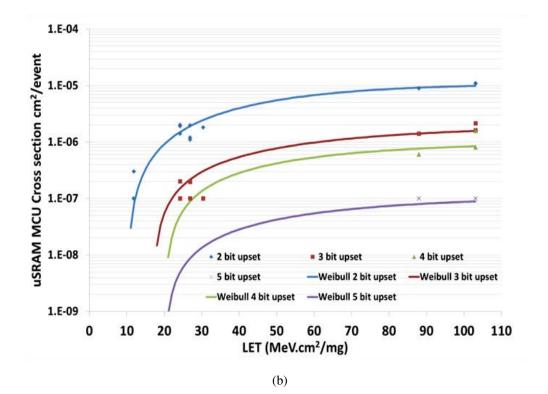

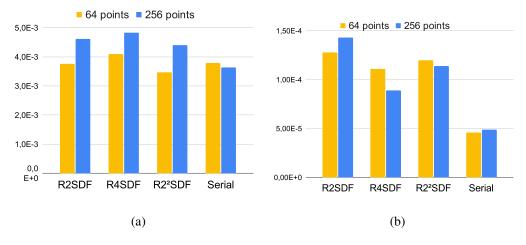

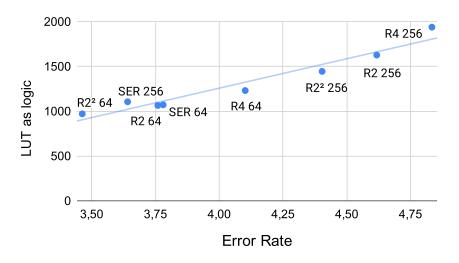

The sensitivity of a circuit is usually measured in terms of its cross section with respect to a given particle, calculated as the ratio between the number of faults found in the test and the amount of ionizing particles per area used in the radiation campaign. This metric is used to estimate the number of faults that will be caused by the radiation over the lifetime of the system, but also to gather data about the effectiveness of the implemented hardening systems and to help improve them. The fault injection method used in this Thesis as a complement to radiation is based on modifying the logic value of the data stored in the configuration memory of the FPGA. This memory stores the description of the operation of the circuit implemented in the FPGA, so modifying its values is equivalent to modifying the circuit. In FPGAs that use SRAM technology in their configuration memories, such as those used in this Thesis, this is the component most sensitive to radiation, so it is possible to compare the results of fault injection and radiation campaigns. Analogously to the cross section, in fault injection experiments we can talk about the error rate, calculated as the ratio between the number of faults found and the amount of memory bits injected.

Throughout this Thesis, different circuits hardened by Triple Modular Redundancy have been developed and their performance has been compared with those of other Approximate Redundancy techniques, namely Reduced Precision Redundancy (RPR), Reduced Resolution Redundancy (RRR) and Optimized Redundancy for Composite Algorithms (ORCA). The latter two are original contributions presented in this Thesis.

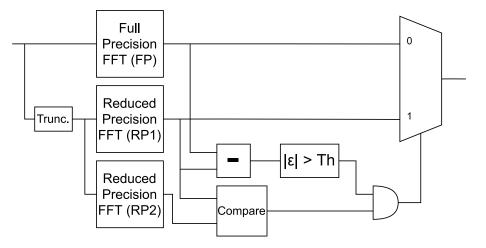

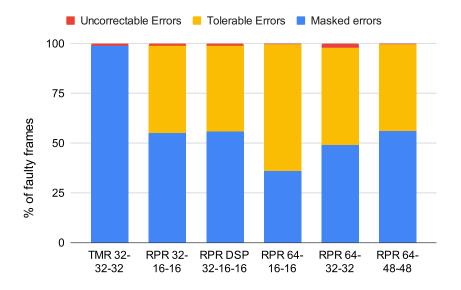

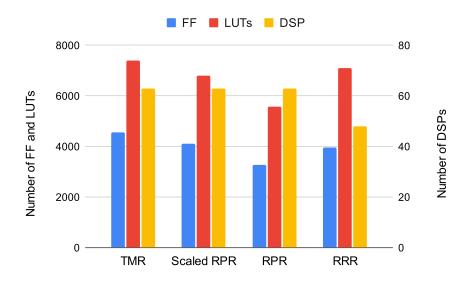

Reduced Precision Redundancy is based on the use of two redundant replicas that compute results with a smaller number of bits than the original circuit. For each output data, the result of the original circuit and the two reduced-precision results are compared. If the two reduced-precision results are identical and their difference with the full-precision result is greater than a certain threshold value, a fault is considered to exist in the original circuit and the reduced-precision result is used to correct it. In any other case, the original result is considered correct, even though it may contain tolerable errors below the comparison threshold. Compared to a TMR-hardened circuit, RPR designs use fewer resources, due to the reduced precision of redundant circuit calculations. However, this also affects the quality of the results obtained when an error is corrected.

In this work we also explore Scaled RPR as a method of obtaining an optimal balance between accuracy and resource consumption. In this variant of the RPR technique, the results of each computational stage in the redundant circuits have a different precision, increasing towards the last stages of the pipeline, where the result has the same accuracy as the original circuit. This method increases the quality of the corrected data while reducing the resources used for hardening.

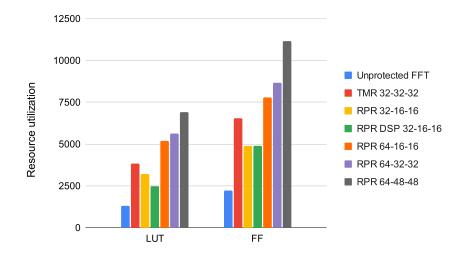

The results of the radiation and fault injection campaigns performed on the RPR hardened designs suggest that the reduction of resources is not only beneficial in terms of resources and energy used by the system, but also leads to a reduction of the sensitivity of the circuits, measured both in cross section and error rate.

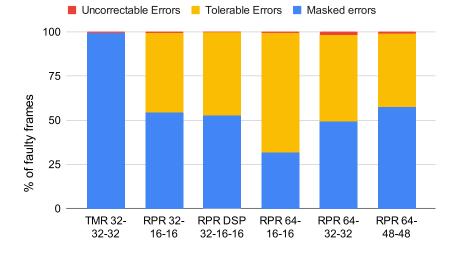

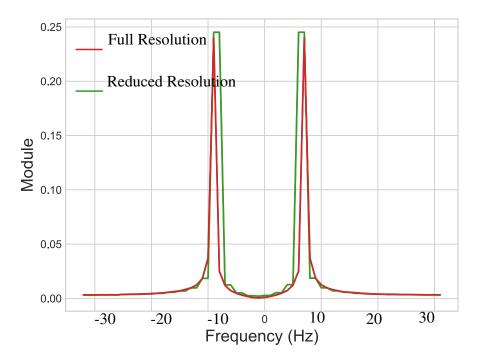

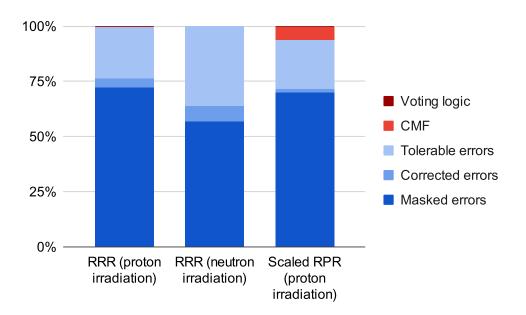

• Reduced Resolution Redundancy is a technique originally proposed in this Thesis. It is suitable for algorithms that work with information in the form of packets whose individual data have some relationship with each other, such as an image processing algorithm. In the RRR technique, two redundant circuits are added that compute the results with a fraction of the original input data. After calculation, the decimated results

can be interpolated to obtain an approximate result of the same size as the result of the original circuit. Once interpolated, the results of the three circuits can be compared to detect and correct faults in a similar way to that used in the RPR technique. By taking advantage of hardware design features, the decrease in the amount of data processed by the Reduced Resolution circuits are translated into a decrease in resources, rather than a decrease in computational time. In this way, the RRR technique is able to reduce resource consumption compared to what would be required if TMR hardening were used.

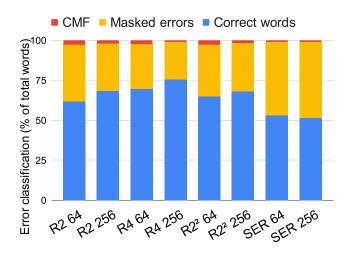

The results of the experiments performed on designs hardened with Reduced Resolution Redundancy suggest that the technique is effective in reducing the resources used and, as in the case of Reduced Precision Redundancy, its sensitivity is also reduced compared to the sensitivity of the same circuit hardened with TMR. In addition, there is a notable reduction in the sensitivity of the circuits to uncorrectable errors, compared to the same result in TMR and RPR. This type of error encompasses those produced by failures in the comparison and voting logic or those in which a single SEU produces failures in the results of two or more of the redundant circuits at the same time, which is known as Common Mode Failure (CMF). However, it is also observed that the quality of the corrections performed using this method worsens slightly.

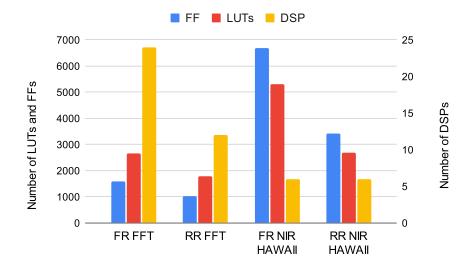

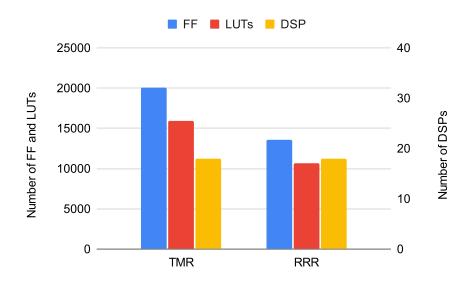

• Optimized Redundancy for Composite Algorithms is also an original contribution of this Thesis. It is suitable for algorithms whose final result can be expressed as the composition of intermediate results computed in previous stages. To harden a circuit using this technique, two redundant circuits are added that are different from each other, each of them processing a different part of the input data set. Each of these approximate circuits computes an intermediate result. The composition of the two intermediate results gives a result identical to that of the original circuit in the absence of faults.

Fault detection is performed by comparing the result of the original circuit with that of the composition of the approximate circuits. In case they are different, the origin of the fault can be determined by comparing the intermediate approximate results against a threshold. If the difference between the intermediate results exceeds the threshold, it means that the fault has occurred in one of the approximate circuits and that the result of the composition should not be used in the output. As with Reduced Precision Redundancy and Reduced Resolution Redundancy, using a comparison threshold implies the existence of tolerable errors. However, this hardening technique allows precise, rather than approximate, corrections to be made in most cases, which improves the quality of the results with respect to other approximate hardening techniques, while reducing the resources used by the hardened system compared to traditional techniques.

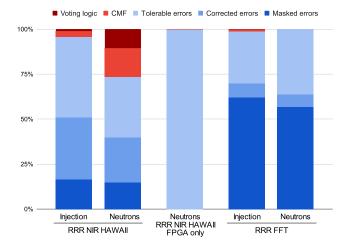

The results of experiments performed with hardened designs using Optimized Redundancy for Composite Algorithms confirm that this hardening technique is capable of producing precise corrections in a high percentage of the events. Its sensitivity to all types of errors and to uncorrectable errors is also diminished compared to that obtained with Triple Modular Redundancy.

The results presented in this Thesis support the idea that Approximate Redundancy techniques are viable alternatives to the usual radiation hardening techniques, provided that the system characteristics tolerate the presence of inaccurate results. Approximate Redundancy manages to reduce the area and resource consumption of hardened circuits at the cost of making approximate corrections, ranging from obtaining lower accuracy in the corrected results (RPR), corrections based on close correct results (RRR) or exact corrections in some cases and lower precision in others (ORCA). In either case, these approximate corrections may be perceived as mere noise by the system and not affect its functionality.

Radiation and fault injection campaigns show that Approximate Hardening techniques reduce the sensitivity of hardened circuits (with respect to that of the same circuit hardened with Triple Modular Redundancy) as a consequence of reduced resources. Comparing the results of both types of campaigns has allowed us to establish a relationship between them, which validates the fault injection method and positions it as a fast and inexpensive way to obtain preliminary results. Fault injection has allowed us, on the one hand, to refine the performance of the proposed techniques without the need to test them in radiation campaigns or long simulation campaigns, and on the other hand, to know in advance the sensitivity and error correction capacity of the proposed hardening techniques. These two advantages have allowed us to carry out a more adequate planning of the radiation campaigns, making the best use of the available radiation time and minimizing the costs of the experiments.

In addition to these features, the results obtained suggest that the way in which the techniques of Reduced Resolution Redundancy and Optimized Redundancy for Composite Algorithms treat the data reduces the incidence of Common Mode Failures, which are responsible for a large part of the uncorrectable failures in all the systems hardened by RHBD techniques.

## LIST OF ACRONYMS

## A

| ABFT  | Algorithm-Based Fault Tolerance. 69                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALD   | Area Limited Design. 99                                                                                                                                                |

| APSoC | All-Programmable System on Chip. 71, 84, 101, 123, 132, 136, 159                                                                                                       |

| ARM   | Advanced RISC Machine. 71, 84, 101, 123, 132, 136                                                                                                                      |

| ASIC  | Application-Specific Integrated Circuit. 17, 19, 37, 59, 69, 96, 169                                                                                                   |

| ATMR  | Approximate Triple Modular Redundancy. 49, 79, 80, 96, 111-113                                                                                                         |

| В     |                                                                                                                                                                        |

| BOX   | Buried OXide. 37                                                                                                                                                       |

| BTMR  | Block Triple Modular Redundancy. 48, 49, 59, 67, 78, 81, 95                                                                                                            |

| BU    | Butterfly Unit. 70, 98, 116                                                                                                                                            |

| C     |                                                                                                                                                                        |

| CLB   | Configurable Logic Block. 83                                                                                                                                           |

| CME   | Coronal Mass Ejection. 8                                                                                                                                               |

| CMF   | Common-Mode Failures. xv, xxi, 19, 60, 68, 69, 71–75, 78, 79, 86, 87, 90–92, 96, 102–104, 106, 121, 123, 125–128, 135, 144, 145, 151, 156, 158, 161, 162, 164, 169–171 |

| CMOS  | Complementary Metal-Oxide Semiconductor. 13, 16, 37-39                                                                                                                 |

| CNA   | Centro Nacional de Aceleradores. ix, xi, xiv, xix, 71, 84, 101, 136, 190                                                                                               |

| COTS  | Commercial Off-The-Shelf. x, xiii, xviii, 2, 22, 28, 29, 57, 61, 65, 66, 68, 111, 128, 150, 151                                                                        |

| CRAND | Cosmic Ray Albedo Neutron Decay. 10                                                                                                                                    |

| D     |                                                                                                                                                                        |

| DD    | Displacement Damage. vii, x, xii, xiii, xviii, xix, 13, 28, 30, 37                                                                                                     |

**DDD** Displacement Damage Dose. 13

| DDR  | Design Diversity Redundancy. 152                                                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------|

| DICE | Dual Interlocked CEll. 54                                                                                               |

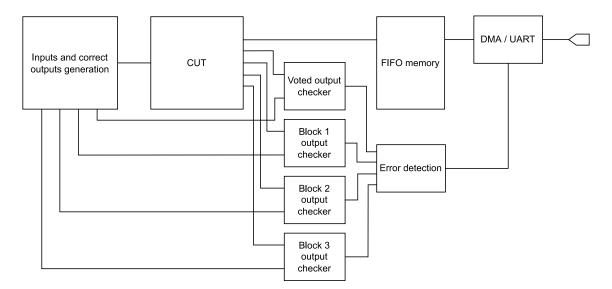

| DMA  | Direct Memory Access. 141, 143, 145, 146, 194                                                                           |

| DMR  | Dual Modular Redundancy. 44, 50                                                                                         |

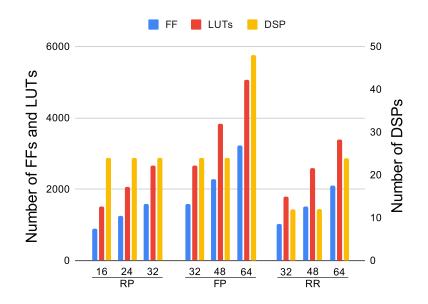

| DSP  | Digital Signal Processing. 3, 49, 67–69, 80, 81, 83, 111, 112, 114, 117, 118, 124, 126, 131–135, 157, 160, 163, 166–168 |

| DT2  | Dual Duplex Tolerant to Transients. 66                                                                                  |

| DTMR | Distributed Triple Modular Redundancy. 46–49, 59, 60, 81                                                                |

| DWC  | Duplication With Comparison. viii, xi, xiii, xix, 44, 50, 112, 166                                                      |

|      |                                                                                                                         |

## E

| ECC   | Error-Correcting Code. 66                                |

|-------|----------------------------------------------------------|

| EDAC  | Error Detection And Correction. 51, 54, 56, 96, 111, 171 |

| ELDRS | Enhanced Low Dose Rate Sensitivity. 12                   |

| ELT   | Enclosed Layout Transistor. 36                           |

| ESA   | European Space Agency. 3, 130, 132, 140                  |

| ESCC  | European Space Components Coordination. 30               |

|       |                                                          |

## F

| FF   | Flip-Flop. 86, 117, 118, 124, 134, 167                                                                                                                                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FFT  | Fast Fourier Transform. 50, 68–73, 75, 76, 78, 79, 81–89, 92, 95, 96, 98–105, 107, 108, 111–113, 115–120, 122–127, 130, 132–140, 142, 143, 145, 150, 154–157, 159–162, 167, 168                                                                                             |

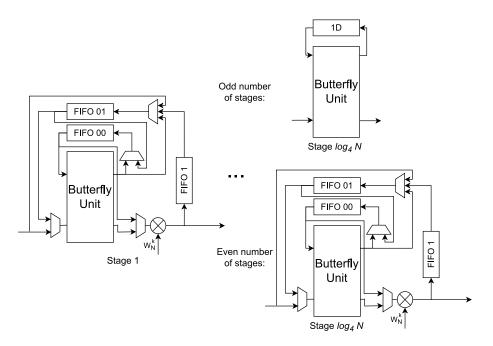

| FIFO | First-In First-Out. 70, 98, 115–118, 137, 194                                                                                                                                                                                                                               |

| FIR  | Finite Impulse Response. 79, 81, 113, 150, 154, 157-159, 163, 164                                                                                                                                                                                                           |

| FIT  | Failure In Time. 27                                                                                                                                                                                                                                                         |

| FMEA | Failure Mode and Effect Analysis. 24                                                                                                                                                                                                                                        |

| FP   | Full Precision. 81-83, 85-89, 97, 100, 112, 117, 118, 151                                                                                                                                                                                                                   |

| FPGA | Field-Programmable Gate Array. viii, xi, xiii, xiv, xix, xx, 2, 3, 5, 17, 19, 37, 43, 46, 48, 51, 56–62, 64–69, 75, 78–81, 84, 96, 97, 101, 108, 117, 121, 123, 125, 127, 130, 131, 134, 136, 144, 145, 150, 151, 156, 157, 159, 161, 165, 167, 169, 171, 190, 191, 193–195 |

| FR   | Full Resolution. 114, 115, 118–122, 126, 133, 135, 137, 138, 141                                                                                                                                                                                                            |

## **FSM** Finite State Machine. 51

# G

| GCR  | Galactic Cosmic Radiation. 10           |

|------|-----------------------------------------|

| GEO  | Geostationary Earth Orbit. 9, 12, 23    |

| GNSS | Global Navigation Satellite Systems. 21 |

| GPIO | General Purpose Input/Output. 192       |

| GTMR | Global Triple Modular Redundancy. 47    |

## H

| HDL   | Hardware Description Language. 58                                                                 |

|-------|---------------------------------------------------------------------------------------------------|

| HIT   | Heavy-Ion Tolerant. 54                                                                            |

| HLS   | High-Level Synthesis. 132, 141                                                                    |

| Ι     |                                                                                                   |

| IEEE  | Institute of Electrical and Electronic Engineers. 130, 150                                        |

| IP    | Intellectual Property. 48, 70, 71, 79, 82, 84, 89, 92, 101, 123, 136, 143, 157, 159, 160, 190–195 |

| ISS   | International Space Station. 9                                                                    |

| K     |                                                                                                   |

| kerma | Kinetic Energy Released to Matter. 13                                                             |

| L     |                                                                                                   |

| LCL   | Latching Current Limiter. 39, 40, 65                                                              |

| LEO   | Low Earth Orbit. 9, 10, 23                                                                        |

| LET   | Linear Energy Transfer. 14, 25                                                                    |

| LTMR  | Local Triple Modular Redundancy. 45–47                                                            |

| LUT   | Look-Up Table. 83, 84, 86, 90, 100, 107, 108, 117, 124, 126, 134, 142, 163, 167, 168              |

|       |                                                                                                   |

LUTRAM Look-Up Table Random Access Memory. 83

Μ

| MBU    | Multiple Bit Upset. 19, 52, 56                                 |

|--------|----------------------------------------------------------------|

| MCU    | Multiple Cell Upset. 19, 69, 102                               |

| MDC    | Multi-path Delay Commutator. 70                                |

| MEO    | Medium Earth Orbit. 9                                          |

| MOSFET | Metal-Oxide-Semiconductor Field-Effect Transistor. 17, 32, 39  |

| MPSoC  | MultiProcessor System-On-Chip. 2, 3, 57, 65, 66, 130, 171, 190 |

| MSE    | Mean Squared Error. 75, 87, 103, 139                           |

| MTBF   | Mean Time Between Failures. 27                                 |

| MTTF   | Mean Time To Failure. 27                                       |

# N

| NASA | National Aeronautics and Space Administration. 21      |

|------|--------------------------------------------------------|

| NIEL | Non Ionizing Energy Loss. 13                           |

| NIR  | Near InfraRed. 132, 135, 136, 140–146                  |

| NMOS | Negative-channel Metal Oxide Semiconductor. 16, 36, 38 |

| NMR  | N-Modular Redundancy. 44, 45, 49, 52, 62               |

| NNI  | Nearest Neighbour Interpolation. 133, 141              |

|      |                                                        |

## 0

**ORCA** Optimized Redundancy for Composite Algorithms. viii, xi, xiv, xvi, xx, xxii, xxxvi, 150, 152–156, 158–165, 168–170

## Р

| PC   | Program Counter. 65                                                                                            |

|------|----------------------------------------------------------------------------------------------------------------|

| PIPB | Propagation-Induced Pulse Broadening. 19                                                                       |

| PL   | Programmable Logic. 132                                                                                        |

| PMOS | Positive-channel Metal Oxide Semiconductor. 16, 38, 43                                                         |

| POA  | Post Oxidation Annealing. 36                                                                                   |

| PS   | Processing System. 132                                                                                         |

| PSNR | Peak Signal-to-Noise Ratio. 68, 75, 87, 88, 91, 103, 104, 106–108, 125, 126, 139, 140, 143, 144, 161, 162, 170 |

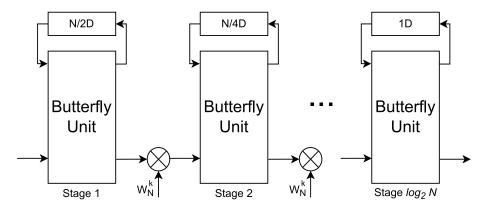

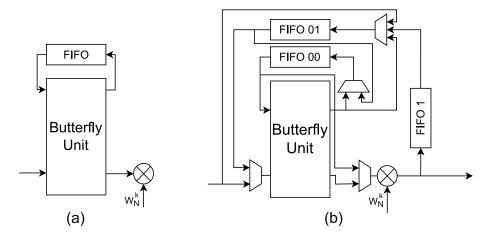

| $\mathbf{R}2^{2}\mathbf{SDF}$ | Radix-2 <sup>2</sup> Singlepath-Delay Feedback. 98, 99, 102                                                                                                                                              |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R2SDF                         | Radix-2 Singlepath-Delay Feedback. 70, 98, 99, 102, 115–117, 123, 156                                                                                                                                    |

| R4SDF                         | Radix-4 Singlepath-Delay Feedback. 70, 98, 99                                                                                                                                                            |

| RAM                           | Random Access Memory. 52, 58, 83, 100                                                                                                                                                                    |

| RHBD                          | Radiation Hardening By Design. vii, viii, x-xiii, xvii-xix, xxii, 22, 37, 39, 61, 131, 151, 171                                                                                                          |

| RHBP                          | Radiation Hardening By Process. vii, x, xii, xviii, 22, 35, 37, 40, 61, 131                                                                                                                              |

| RoRa                          | Reliability-oriented place and Route Algorithm. 60                                                                                                                                                       |

| RP                            | Reduced Precision. 81-83, 85-89, 91, 92, 97, 100, 103, 107, 112, 117, 118                                                                                                                                |

| <b>RP-TMR</b>                 | Reduced Precision Triple Modular Redundancy. 79, 81, 82, 84, 92                                                                                                                                          |

| RPR                           | Reduced Precision Redundancy. viii, xi, xiv-xvi, xx-xxii, 4, 49, 50, 79, 81–83, 85–89, 91, 92, 96–108, 111–114, 117–119, 122–124, 126, 127, 131, 132, 135, 137–140, 147, 151–153, 160–164, 166, 167, 170 |

| RR                            | Reduced Resolution. xxxv, 114, 115, 117–122, 127, 133, 135, 137, 138, 141                                                                                                                                |

| RRR                           | Reduced Resolution Redundancy. viii, xi, xiv, xvi, xx–xxii, xxxv, 113–115, 117, 118, 122–127, 130, 132–147, 152, 156, 160–162, 167–170                                                                   |

| RTS                           | Random Telegraph Signal. 13                                                                                                                                                                              |

| S                             |                                                                                                                                                                                                          |

| SAA                           | South Atlantic Anomaly. 10                                                                                                                                                                               |

| SDC                           | Single-path Delay Commutator. 70                                                                                                                                                                         |

| SDF                           | Single-path Delay Feedback. 70, 98, 115–117, 122                                                                                                                                                         |

| SEB                           | Single Event Burnout. 17                                                                                                                                                                                 |

| SECDEC                        | Single Error Correction - Double Error Correction. 55                                                                                                                                                    |

| SEDR                          | Single Event Dielectric Rupture. 17                                                                                                                                                                      |

| SEE                           | Single Event Effects. vii, x, xii, xiii, xviii, xix, 14, 25, 31–35, 58, 65, 96                                                                                                                           |

| SEFI                          | Single Event Functional Interrupt. 18–20, 64                                                                                                                                                             |

| SEGR                          | Single Event Gate Rupture. 17                                                                                                                                                                            |

| SEHE                          | Single Event Hard Error. 17                                                                                                                                                                              |

| SEL                           | Single Event Latch-up. 16, 37, 64                                                                                                                                                                        |

| SEM                           | Soft Error Mitigation. 71, 84, 89, 101, 143, 193–195                                                                                                                                                     |

| SEP                           | Solar Energetic Particles. 8                                                                                                                                                                             |

| SESB    | Single Event Snapback. 16                                                                                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SET     | Single Event Transient. 18, 19, 34, 38, 40–43, 50, 52, 96                                                                                                                                                                                        |

| SEU     | Single Event Upset. xiv, xv, 18, 19, 33, 34, 38, 43, 46–48, 51, 53, 56, 58–60, 64, 69, 96, 97                                                                                                                                                    |

| SoC     | System On Chip. 71, 84, 101, 123                                                                                                                                                                                                                 |

| SOI     | Silicon On Insulator. 37, 38, 40                                                                                                                                                                                                                 |

| SPA     | Single Photon Absorption. 34                                                                                                                                                                                                                     |

| SPENVIS | SPace ENVironment Information System. 28                                                                                                                                                                                                         |

| SRAM    | Static Random Access Memory. xiv, 5, 19, 20, 52, 58, 59, 61, 64, 69, 75, 80, 81, 96, 156                                                                                                                                                         |

| STI     | Shallow Trench Isolation. 36                                                                                                                                                                                                                     |

| Т       |                                                                                                                                                                                                                                                  |

| TID     | Total Ionizing Dose. vii, x, xii, xiii, xviii, xix, 11–13, 28, 30, 35–38, 40, 62                                                                                                                                                                 |

| TMR     | Triple Modular Redundancy. viii, xi, xiii–xv, xix–xxi, 44, 45, 48–51, 59–62, 67–69, 71, 79–83, 85–89, 91, 92, 95–98, 100–106, 108, 111–113, 117, 118, 123, 124, 126, 127, 133, 137–139, 142, 146, 150–152, 156, 159–164, 166, 167, 169, 170, 194 |

| TPA     | Two Photon Absorption. 34                                                                                                                                                                                                                        |

| U       |                                                                                                                                                                                                                                                  |

| UART    | Universal Asynchronous Receiver-Transmitter. 71, 101, 123, 191, 194, 195                                                                                                                                                                         |

| USA     | United States of America. 21                                                                                                                                                                                                                     |

| USB     | Universal Serial Bus. 191                                                                                                                                                                                                                        |

| USSR    | Union of Sovietic Socialist Republics. 21                                                                                                                                                                                                        |

| V       |                                                                                                                                                                                                                                                  |

**VHDL** Very High Speed Integrated Circuits Hardware Description Language. 51, 58

## **CONTENTS**

| ACKNOWLEDGEMENTS                                    | iii   |

|-----------------------------------------------------|-------|

| PUBLISHED AND SUBMITTED CONTENT                     | iv    |

| OTHER RESEARCH MERITS                               | vi    |

| RESUMEN NO TÉCNICO                                  | vii   |

| NON-TECHNICAL SUMMARY                               | X     |

| RESUMEN TÉCNICO                                     | xii   |

| TECHNICAL SUMMARY                                   | viii  |

| LIST OF ACRONYMS                                    | xiii  |

| ACRONYMS                                            | xviii |

| 1. INTRODUCTION                                     | 1     |

| 1.1. Problem statement                              | 1     |

| 1.2. Aim and scope                                  | 2     |

| 1.3. Methodology                                    | 3     |

| 1.4. Significance                                   | 4     |

| 1.5. Funding                                        | 5     |

| 1.6. Document overview                              | 5     |

| 2. STATE OF THE ART                                 | 7     |

| 2.1. Ionizing radiation in the space environment    | 7     |

| 2.1.A. Sources of radiation                         | 7     |

| 2.2. Effects on electronics                         | 11    |

| 2.2.A. Total Ionizing Dose                          | 11    |

| 2.2.B. Displacement Damage                          | 13    |

| 2.2.C. Single Event Effects                         | 14    |

| 2.3. Space Industry                                 | 21    |

| 2.4. Dependability and qualification                | 23    |

| 2.4.A. Dependability                                | 23    |

| 2.4.B. Radiation Hardness Assurance: Qualification. | 28    |

| 2.5. Hardening against radiation                                                               | 35 |

|------------------------------------------------------------------------------------------------|----|

| 2.5.A. TID hardening                                                                           | 35 |

| 2.5.B. DD hardening                                                                            | 37 |

| 2.5.C. SEL hardening                                                                           | 37 |

| 2.5.D. SET hardening                                                                           | 40 |

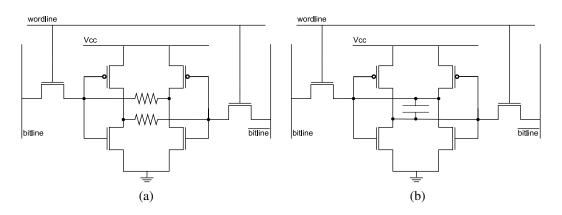

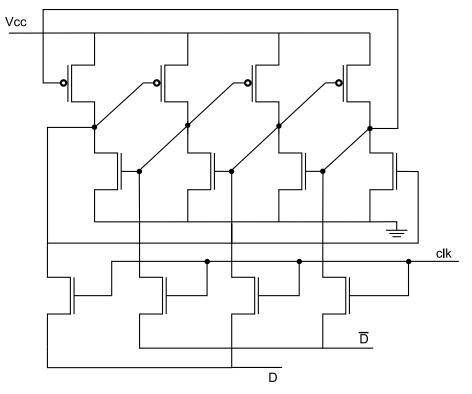

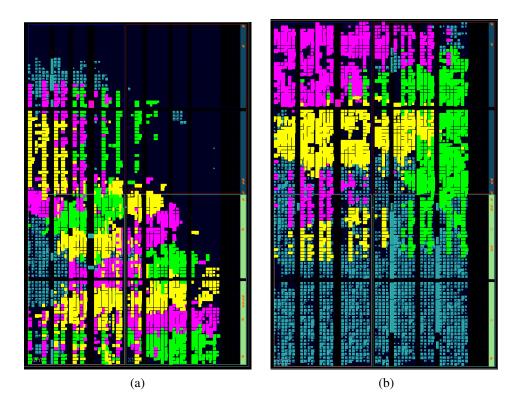

| 2.5.E. SEU hardening                                                                           | 43 |

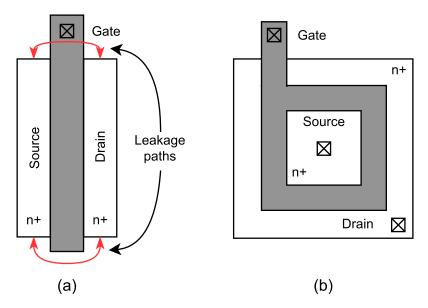

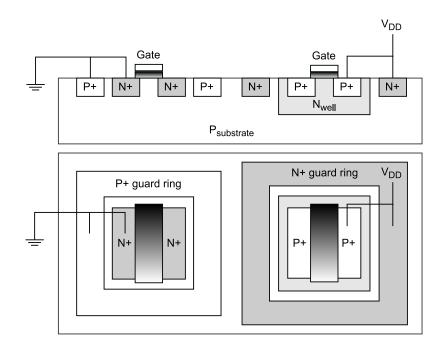

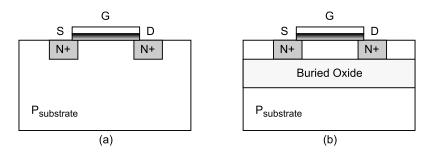

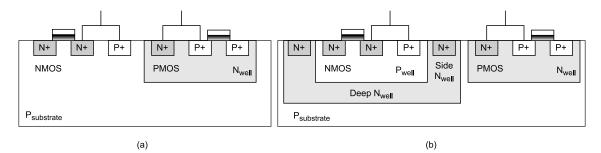

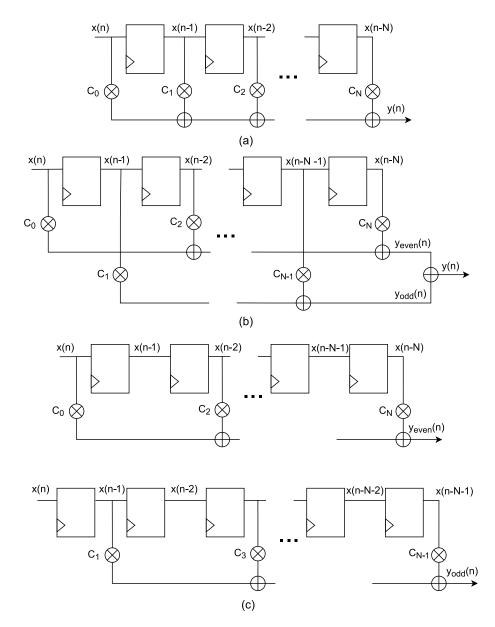

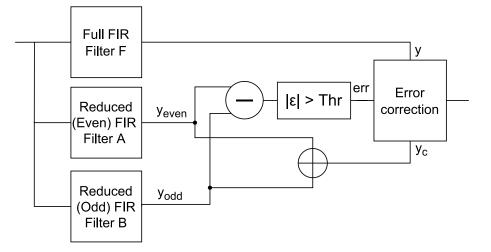

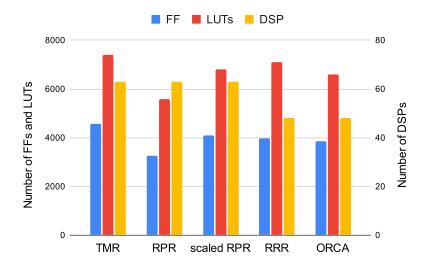

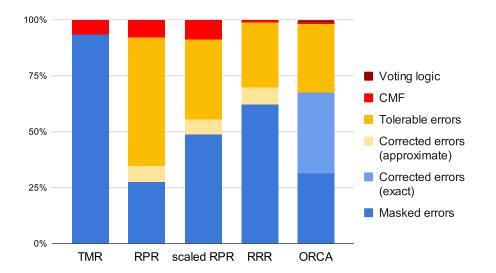

| 2.6. Hardening against SEUs                                                                    | 43 |