PHD THESIS

# Parallel source code transformation techniques using design patterns

#### **Author:**

David del Río Astorga

#### **Advisor:**

José Daniel García Sánchez

**Computer Science and Technology**

Leganés, July 2018.

### PhD Thesis

# Parallel source code transformation techniques using design patterns

Advisor: José Daniel García Sánchez

David del Río Astorga

**Author:**

El Presidente

| Computer Science and Technology |    |                                          |  |  |  |  |  |

|---------------------------------|----|------------------------------------------|--|--|--|--|--|

| Presidente                      | D. |                                          |  |  |  |  |  |

| Vocal                           | D. |                                          |  |  |  |  |  |

| Secretario                      | D. |                                          |  |  |  |  |  |

|                                 |    |                                          |  |  |  |  |  |

|                                 |    |                                          |  |  |  |  |  |

| Realizado el acto de c          |    | sa y la lectura de tesis en en el dia de |  |  |  |  |  |

| Calificación:                   |    |                                          |  |  |  |  |  |

|                                 |    |                                          |  |  |  |  |  |

El Secretario

Los Vocales

## **Abstract**

In recent years, the traditional approaches for improving performance, such as increasing the clock frequency, has come to a dead-end. To tackle this issue, parallel architectures, such as multi-/many-core processors, have been envisioned to increase the performance by providing greater processing capabilities. However, programming efficiently for this architectures demands big efforts in order to transform sequential applications into parallel and to optimize such applications. Compared to sequential programming, designing and implementing parallel applications for operating on modern hardware poses a number of new challenges to developers such as data races, deadlocks, load imbalance, etc.

To pave the way, parallel design patterns provide a way to encapsulate algorithmic aspects, allowing users to implement robust, readable and portable solutions with such high-level abstractions. Basically, these patterns instantiate parallelism while hiding away the complexity of concurrency mechanisms, such as thread management, synchronizations or data sharing. Nonetheless, frameworks following this philosophy does not share the same interface and users require understanding different libraries, and their capabilities, not only to decide which fits best for their purposes but also to properly leverage them. Furthermore, in order to parallelize these applications, it is necessary to analyze the sequential code in order to detect the regions of code that can be parallelized that is a time consuming and complex task. Additionally, different libraries targeted to specific devices provide some algorithms implementations that are already parallel and highly-tuned. In these situations, it is also necessary to analyze and determine which routine implementation is the most suitable for a given problem.

To tackle these issues, this thesis aims at simplifying and minimizing the necessary efforts to transform sequential applications into parallel. This way, resulting codes will improve their performance by fully exploiting the available resources while the development efforts will be considerably reduced. Basically, in this thesis, we contribute with the following. First, we propose a technique to detect potential parallel patterns in sequential code. Second, we provide a novel generic C++ interface for parallel patterns which acts as a switch among existing frameworks. Third, we implement a framework that is able to transform sequential code into parallel using the proposed pattern discovery technique and pattern interface. Finally, we propose mechanisms that are able to select the most suitable device and routine implementation to solve a given problem based on previous performance information. The evaluation demonstrates that using the proposed techniques can minimize the refactoring and optimization time while improving the performance of the resulting applications with respect to the original code.

### Resumen

En los últimos años, las técnicas tradicionales para mejorar el rendimiento, como es el caso del incremento de la frecuencia de reloj, han llegado a sus límites. Con el fin de seguir mejorando el rendimiento, se han desarrollado las arquitecturas paralelas, las cuales proporcionan un incremento del rendimiento al estar provistas de mayores capacidades de procesamiento. Sin embargo, programar de forma eficiente para estas arquitecturas requieren de grandes esfuerzos por parte de los desarrolladores. Comparado con la programación secuencial, diseñar e implementar aplicaciones paralelas enfocadas a trabajar en estas arquitecturas presentan una gran cantidad de dificultades como son las condiciones de carrera, los deadlocks o el incorrecto balanceo de la carga.

En este sentido, los patrones paralelos son una forma de encapsular aspectos algorítmicos de las aplicaciones permitiendo el desarrollo de soluciones robustas, portables y legibles gracias a las abstracciones de alto nivel. En general, estos patrones son capaces de proporcionar el paralelismo a la vez que ocultan las complejidades derivadas de los mecanismos de control de concurrencia necesarios como el manejo de los hilos, las sincronizaciones o la compartición de datos. No obstante, los diferentes frameworks que siguen esta filosofía no comparten una única interfaz lo que conlleva que los usuarios deban conocer múltiples bibliotecas y sus capacidades, con el fin de decidir cuál de ellos es mejor para una situación concreta y como usarlos de forma eficiente. Además, con el fin de paralelizar aplicaciones existentes, es necesario analizar e identificar las regiones del código que pueden ser paralelizadas, lo cual es una tarea ardua y compleja. Además, algunos algoritmos ya se encuentran implementados en paralelo y optimizados para arquitecturas concretas en diversas bibliotecas. Esto da lugar a que sea necesario analizar y determinar que implementación concreta es la más adecuada para solucionar un problema dado.

Para paliar estas situaciones, está tesis busca simplificar y minimizar el esfuerzo necesario para transformar aplicaciones secuenciales en paralelas. De esta forma, los códigos resultantes serán capaces de explotar los recursos disponibles a la vez que se reduce considerablemente el esfuerzo de desarrollo necesario. En general, esta tesis contribuye con lo siguiente. En primer lugar, se propone una técnica de detección de patrones paralelos en códigos secuenciales. En segundo lugar, se presenta una interfaz genérica de patrones paralelos para C++ que permite seleccionar la implementación de dichos patrones proporcionada por frameworks ya existentes. En tercer lugar, se introduce un framework de transformación de código secuencial a paralelo que hace uso de las técnicas de detección de patrones y la interfaz presentadas. Finalmente, se proponen mecanismos capaces de seleccionar la implementación más adecuada para solucionar un problema concreto basándose en el rendimiento obtenido en ejecuciones previas. Gracias a la evaluación realizada se ha podido demostrar que uso de las técnicas presentadas pueden minimizar el tiempo necesario para transformar y optimizar el código a la vez que mejora el rendimiento de las aplicaciones transformadas.

# Agradecimientos

Esta tesis cierra una etapa de mi vida la cual he compartido con muchas personas a las que quiero agradecer su apoyo y compañía. Estos agradecimientos van para todas estas personas que han estado ahí en todo momento, tanto en el ámbito profesional como personal.

En primer lugar, me gustaría agradecer todo el esfuerzo y apoyo proporcionado por mis compañeros de trabajo, tanto en el propio trabajo como aguantándome durante este tiempo. A Manuel por los días de duro trabajo para sacar adelante las publicaciones antes de las fechas límite, por enseñarme a como ser mejor en nuestra profesión y por las risas en los momentos de distensión. A Javi Doc por compartir su sabiduría y conocimiento cada día sobre todos los temas existentes. A Luismi que me ayudo en los primeros pasos y animando el ambiente con sus chistes (exageradamente malos). No sin mencionar a todos los compañeros con los que he compartido laboratorio en los días buenos y malos: Javi "Kernel", Andrés, Mario, Guille y Javi Prieto. Gracias a vosotros he podido disfrutar del trabajo realizado. También quiero agradecer la acogida que se me ha dado en este grupo y a mi director José Daniel por darme la oportunidad de trabajar en este proyecto.

Por otro lado, quiero agradecer a mi familia el haberme dado el apoyo durante todo este periodo universitario, desde que inicie mis estudios en Ingeniería Informática hasta el día de hoy en que finalizo esta tesis. También quiero agradecer a Noelia el haber estado para mí en los momentos buenos y en los no tan buenos, siendo la mejor compañera que haya podido conocer en todos los aspectos. Finalmente, no puedo olvidarme de todos los amigos que me han acompañado en este largo camino y con los que tanto he compartido. A Javi, Juan, Raúl, Iván y un largo etcétera. Muchas gracias a todos.

# **Contents**

| A۱ | bstrac | t                                                | iii          |

|----|--------|--------------------------------------------------|--------------|

| Re | esume  | n                                                | $\mathbf{v}$ |

| Ą  | grade  | rimientos                                        | vii          |

| 1  | Intr   | oduction                                         | 1            |

|    | 1.1    | Motivation                                       | 1            |

|    | 1.2    | Objetives                                        | 2            |

|    | 1.3    | Document structure                               | 3            |

| 2  | Stat   | of the art                                       | 5            |

|    | 2.1    | Parallel architectures                           | 5            |

|    | 2.2    | Parallel Programming Models                      | 7            |

|    |        | 2.2.1 Types of parallelism                       | 7            |

|    |        | 2.2.2 Low-level parallel frameworks              | 8            |

|    |        | 2.2.3 High-level parallel frameworks             | 9            |

|    | 2.3    | Parallel Patterns                                | 11           |

|    |        | 2.3.1 Data parallel patterns                     | 12           |

|    |        | 2.3.2 Task parallel patterns                     | 12           |

|    |        | 2.3.3 Stream parallel patterns                   | 13           |

|    |        | 2.3.4 Stream operators                           | 14           |

|    |        | 2.3.5 Advanced stream parallel patterns          | 16           |

|    | 2.4    | Parallel region detection techniques             | 17           |

|    |        | 2.4.1 Dynamic approaches                         | 18           |

|    |        | 2.4.2 Static approaches                          | 19           |

|    | 2.5    | Routine implementation selection techniques      | 19           |

|    | 2.6    | Summary                                          | 20           |

| 3  | Stat   | c parallel pattern detection                     | 23           |

|    |        | LLVM infrastructure and the Abstract Syntax Tree |              |

|    | 3.2    | Parallel Pattern Annotation Specificaction       |              |

|    | 3.3    | Parallel Pattern Analyzer Tool                   |              |

|    | 0.0    | 3.3.1 Pipeline Detection Module                  |              |

|    |        | 3.3.2 Farm Detection Module                      | 28           |

|    |        | 3.3.3 Map Detection Module                       | 28           |

|    | 3.4    | Evaluation                                       | 29           |

|    | 0.1    | 3.4.1 Reference platform                         | 29           |

|    |        | 3.4.2 Results for the benchmarks suites          | 29           |

|    |        | 3.4.3 Analysis of the Fastflow use case          | 31           |

|    | 3.5    | Summary                                          | 32           |

| 4 | Gen | ieric Pa | rallel Pattern Interface                                      | 33           |

|---|-----|----------|---------------------------------------------------------------|--------------|

|   | 4.1 | Execu    | t <mark>tion policies</mark>                                  | 33           |

|   | 4.2 | Comn     | nunication channels                                           | 35           |

|   | 4.3 | Descr    | iption of the pattern interfaces                              | 37           |

|   |     |          | Data patterns                                                 |              |

|   |     | 4.3.2    | Stream patterns                                               | 38           |

|   |     | 4.3.3    | Stream operators                                              | 40           |

|   | 4.4 | Adva     | nced patterns                                                 | 42           |

|   | 4.5 |          | rn composability                                              | 43           |

|   | 4.6 |          | ation                                                         | 49           |

|   |     | 4.6.1    | Reference platform                                            | 51           |

|   |     | 4.6.2    | Analysis of the usability                                     |              |

|   |     | 4.6.3    | Performance analysis of pattern compositions                  |              |

|   |     | 4.6.4    | Performance analysis of stream vs data patterns               |              |

|   |     | 4.6.5    | Performance analysis on heterogeneous configurations          |              |

|   |     | 4.6.6    | Performance analysis of the FM-Radio                          |              |

|   |     | 4.6.7    | Performance analysis of the Stream-Pool pattern               | 56           |

|   |     | 4.6.8    | Performance analysis of the Windowed-Farm pattern             |              |

|   |     |          | Analysis of the <i>count-based</i> windowing policy           |              |

|   |     |          | Analysis of the <i>delta-based</i> windowing policy           |              |

|   |     |          | Analysis of the <i>time-based</i> windowing policy            |              |

|   |     |          | Analysis of the <i>punctuation-based</i> windowing policy     | 59           |

|   |     | 4.6.9    |                                                               | 60           |

|   | 4.7 | Sumn     | nary                                                          | 61           |

| _ | A 1 |          | I Datama hara I Dafasta da a                                  | (2           |

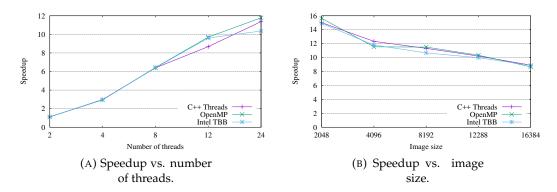

| 5 |     |          | l Patern-based Refactoring                                    | <b>63</b> 63 |

|   | 5.1 |          | el Pattern Refactoring Tool                                   |              |

|   | 5.2 |          | ne Stage Balancing Algorithm                                  | 64           |

|   |     | 5.2.1    |                                                               | 66           |

|   |     | 5.2.2    | 1 1                                                           | 66           |

|   |     | 5.2.3    | The hybrid approach                                           | 68           |

|   |     | 5.2.4    | Finding the optimal concurrency degree                        |              |

|   |     |          | Iterative search                                              |              |

|   | г о | T1       | Greedy iterative search                                       | 70           |

|   | 5.3 |          | ation                                                         | 72<br>72     |

|   |     | 5.3.1    | Reference platform                                            |              |

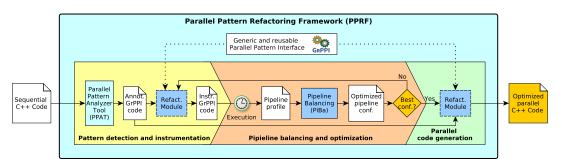

|   |     | 5.3.2    | Analysis of the Pipeline stage balancing algorithm            | 73           |

|   |     | 5.3.3    | Analysis of the optimal concurrency degree search algorithms. | 73           |

|   |     | 5.3.4    | Evaluation with VIDEO-BENCH, a video streaming application    | 75<br>76     |

|   |     |          | Performance evaluation                                        | 76           |

|   |     | Гог      | Fine-grain analysis                                           | 78           |

|   | 5.4 | 5.3.5    | Evaluation of LANE-DETECTION                                  | 80<br>81     |

|   | 3.4 | Sullill  | lary                                                          | 01           |

| 6 | Aut | omatic   | implementation selection techniques                           | 83           |

|   | 6.1 | Comp     | oiletime Implementation Selection                             | 84           |

|   |     | 6.1.1    | Formal definition of the selection algorithm                  | 84           |

|   |     | 6.1.2    | Description of the framework                                  | 85           |

|   |     | 6.1.3    | The profile-guided selection algorithm                        | 87           |

|   |     | 6.1.4    | Working example                                               | 89           |

|   | 6.2 | Evalu    | ation                                                         | 90           |

|   |     | 6.2.1  | Referen   | ice platf | orm    |       |      |     |     |     |    |  |  | <br> |   |  | 91 |

|---|-----|--------|-----------|-----------|--------|-------|------|-----|-----|-----|----|--|--|------|---|--|----|

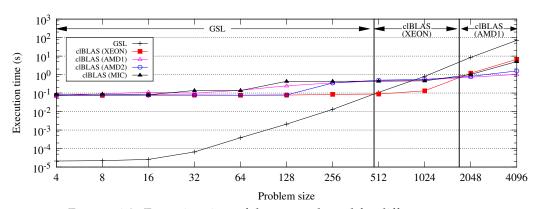

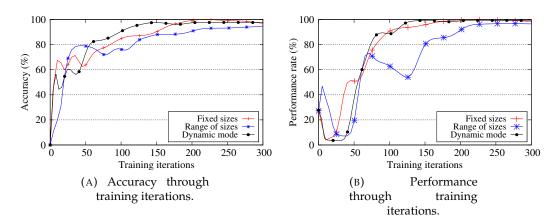

|   |     | 6.2.2  | Analysi   | is with t | he G   | EMM   | use  | cas | e   |     |    |  |  | <br> |   |  | 91 |

|   |     | 6.2.3  | Analysi   | is with t | he H   | ARDI  | use  | cas | e   |     |    |  |  | <br> |   |  | 92 |

|   |     | 6.2.4  | Compa     | rison w   | ith al | terna | tive | app | oro | ach | es |  |  | <br> |   |  | 93 |

|   | 6.3 | Summ   | nary      |           |        |       |      |     |     |     |    |  |  | <br> |   |  | 94 |

| 7 |     |        | ns and fu |           |        |       |      |     |     |     |    |  |  |      |   |  | 95 |

|   | 7.1 | Contr  | ibutions  |           |        |       |      |     |     |     |    |  |  | <br> |   |  | 95 |

|   | 7.2 | Disem  | ination   |           |        |       |      |     |     |     |    |  |  | <br> |   |  | 96 |

|   |     |        |           |           |        |       |      |     |     |     |    |  |  |      |   |  |    |

|   | 7.3 | Future | e work .  |           |        |       |      |     | •   |     |    |  |  | <br> | • |  | 98 |

# **List of Figures**

| 2.1  | Data parallel patterns.                                                                      | 13 |

|------|----------------------------------------------------------------------------------------------|----|

| 2.2  | Stream parallel patterns                                                                     | 15 |

| 2.3  | Stream operators                                                                             | 16 |

| 2.4  | Advanced parallel patterns                                                                   | 17 |

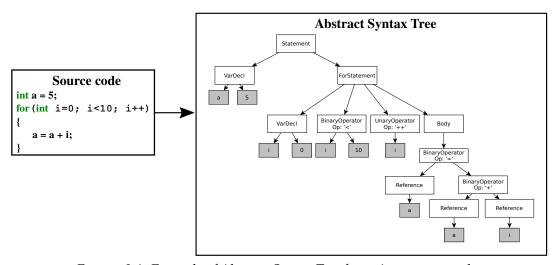

| 3.1  | Example of Abstract Syntax Tree for a given source code                                      | 24 |

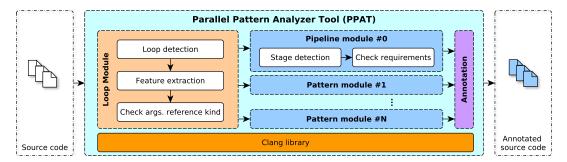

| 3.2  | Workflow diagram of PPAT                                                                     | 25 |

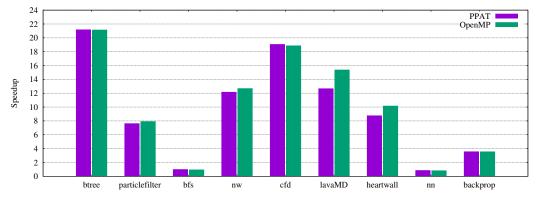

| 3.3  | Execution time of sequential, transformed PPAT code and OpenMP versions of Rodinia benchmark | 31 |

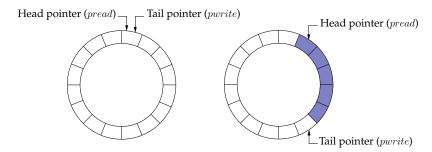

| 4.1  | Schema of the circular buffer queue.                                                         | 36 |

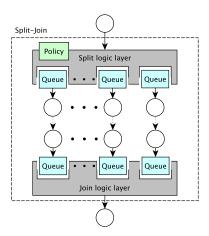

| 4.2  | Schema of the Split-Join communication channels                                              | 41 |

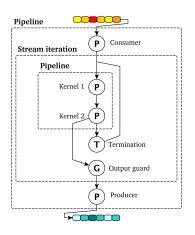

| 4.3  | Example of Pipeline-Stream-Iterator-Pipeline composition in GRPPI                            | 44 |

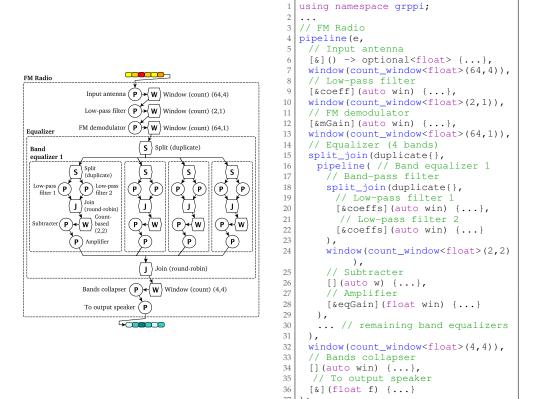

| 4.4  | Pattern composition and implementation of the FM-Radio in GRPPI                              | 45 |

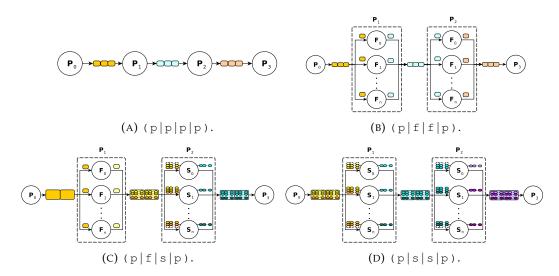

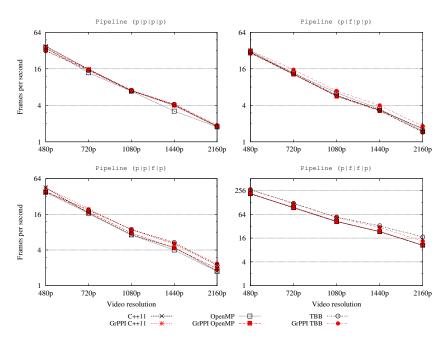

| 4.5  | Pipeline compositions of the video application                                               | 50 |

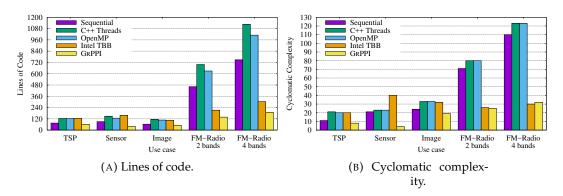

| 4.6  | Lines of code and cyclomatic complexity of the use cases w.r.t different                     |    |

|      | programming models                                                                           | 52 |

| 4.7  | GRPPI and Intel TBB implementations of the FM-Radio                                          | 53 |

| 4.8  | FPS w/ and w/o using GRPPI along with the different frameworks                               |    |

|      | and Pipeline compositions                                                                    | 54 |

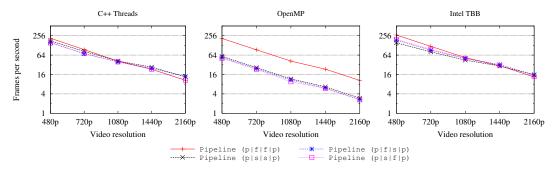

| 4.9  | FPS for different frameworks and Pipeline compositions with stream                           |    |

|      | and data patterns                                                                            | 54 |

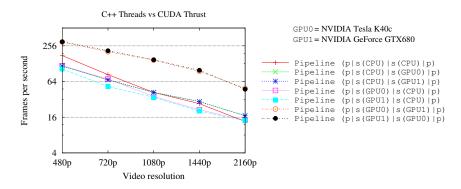

| 4.10 | FPS for the Pipeline composed of two Stencil patterns on different het-                      |    |

|      | erogeneous configurations.                                                                   | 55 |

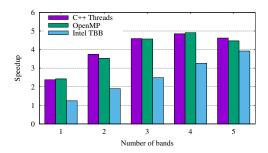

|      | Speedup of the FM-Radio with varying number of bands                                         | 56 |

| 4.12 | Stream-Pool speedup varying with varying number of threads and                               |    |

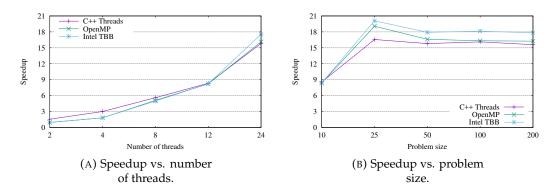

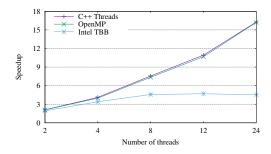

|      | problem size                                                                                 | 57 |

| 4.13 | Windowed-Farm speedup with varying number of threads and win-                                |    |

|      | dow size using <i>count-based</i> windows                                                    | 58 |

| 4.14 | Windowed-Farm speedup with varying number of threads and win-                                |    |

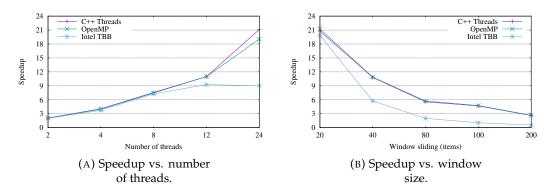

|      | dow size using delta-based windows.                                                          | 59 |

| 4.15 | Windowed-Farm speedup with varying number of threads and win-                                |    |

|      | dow size using <i>time-based</i> windows.                                                    | 60 |

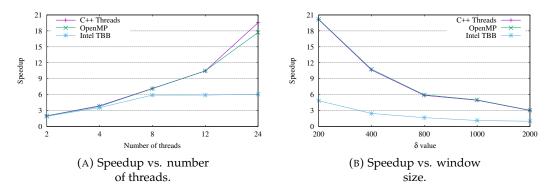

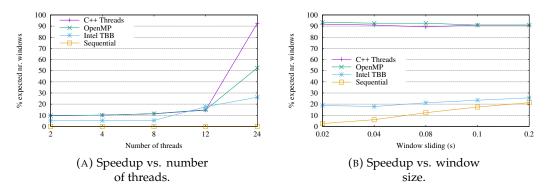

| 4.16 | Windowed-Farm speedup with varying number of threads using punctua                           |    |

|      | based windows                                                                                | 60 |

| 4.17 | Stream-Iterator speedup with varying number of threads and image                             |    |

|      | size                                                                                         | 61 |

| 5.1  | Workflow of the Parallel Pattern Refactoring Framework                                       | 63 |

| 5.2  | Analysis of the maximum concurrency degree using representative                              |    |

|      | pipelines                                                                                    | 69 |

| 5.3  | Automatic approaches for finding the optimal concurrency degree of                           |    |

|      | PIBA balanced Pipelines                                                                      | 70 |

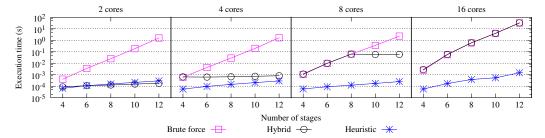

| 5.4  | Time-to-solution of the basic PIBA algorithms.                          | 73 |

|------|-------------------------------------------------------------------------|----|

| 5.5  | Speedup of the of Pipelines in PIPE-BENCH balanced with the basic       |    |

|      | PIBA algorithm variants                                                 | 74 |

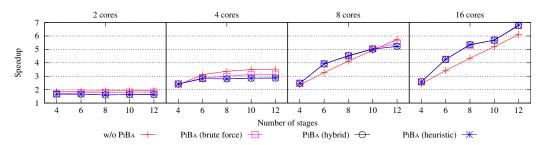

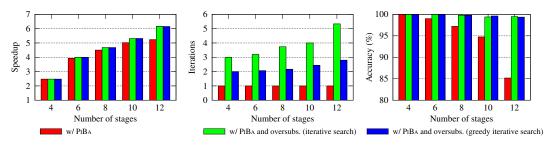

| 5.6  | Comparative of the speedup, number of iterations and accuracy of the    |    |

|      | basic PIBA w.r.t the extended versions for finding the optimal concur-  |    |

|      | rency degree                                                            | 74 |

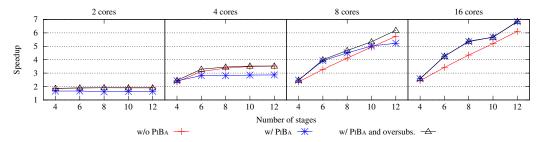

| 5.7  | Speedup of the of Pipelines in PIPE-BENCH balanced with the ex-         |    |

|      | tended PIBA algorithms for oversubscribed scenarios                     | 75 |

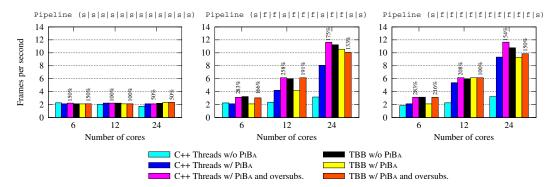

| 5.8  | Frames per second obtained by the different Pipeline variants of VIDEO- |    |

|      | BENCH using C++ threads and Intel TBB GRPPI backends and the            |    |

|      | basic and extended PIBA algorithms                                      | 77 |

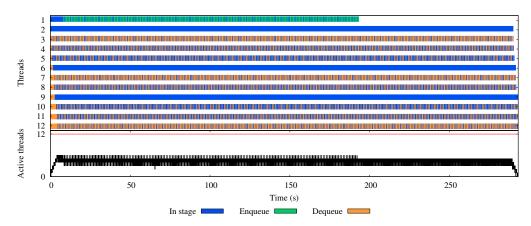

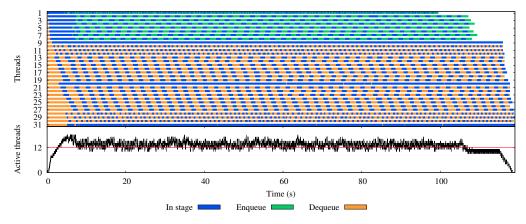

| 5.9  | Task trace and number of active threads during the execution of the     |    |

|      | application without PIBA                                                | 78 |

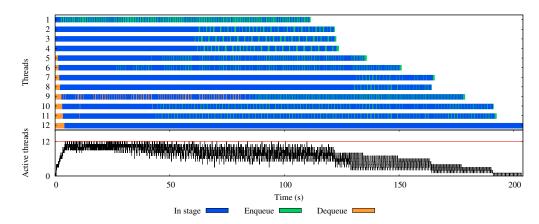

| 5.10 | Task trace and number of active threads during the execution of the     |    |

|      | application with the basic PIBA algorithm.                              | 79 |

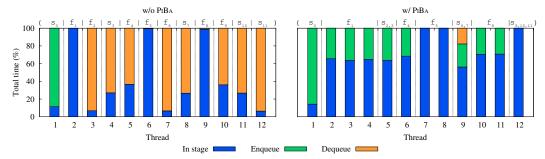

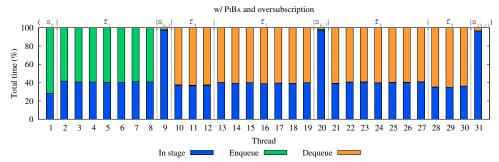

| 5.11 | State time percentage per thread/stage of the VIDEO-BENCHPipeline       |    |

|      | w/o and w/ the basic PIBA algorithm                                     | 79 |

| 5.12 | Task trace and number of active threads during the execution of the     |    |

|      | application with the extended PIBA algorithm                            | 79 |

| 5.13 | State time percentage per thread/stage of the VIDEO-BENCHPipeline       |    |

|      | using the extended PIBA algorithm.                                      | 80 |

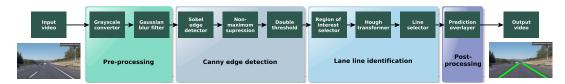

|      | LANE-DETECTION application workflow.                                    | 80 |

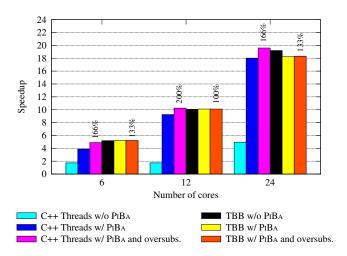

| 5.15 | Speedup obtained by LANE-DETECTION using C++ threads and Intel          |    |

|      | TBB GRPPI back ends and the basic and extended PIBA algorithms          | 81 |

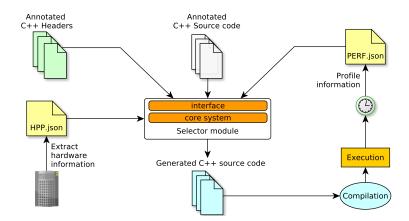

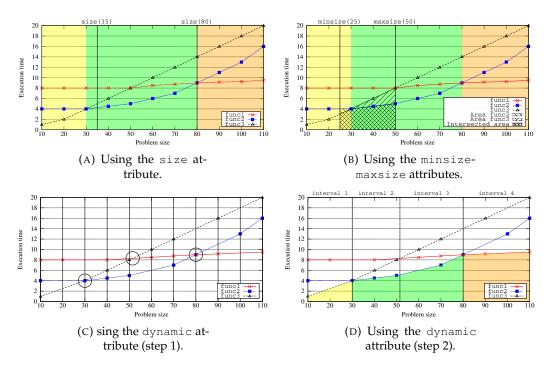

| 6.1  | The best of static demands involve antation would are                   | 07 |

| 6.2  | The hybrid static-dynamic implementation workflow                       | 86 |

| 0.2  | offering three different implementations (func1, func2 and func3).      |    |

|      | Note the cutoffs for problem sizes 30 and 80 between the implemen-      |    |

|      | tations 1–2 and 2–3, respectively.                                      | 89 |

| 6.3  | Execution time of the dgemm kernel for different square matrix sizes    | 09 |

| 0.5  | and implementations                                                     | 91 |

| 6.4  | Progress of the accuracy of the selector and dgemm performance through  | 71 |

| 0.4  | training iterations                                                     | 92 |

| 6.5  | Progress of the accuracy using a range of sizes                         | 93 |

| 6.6  | Execution progress of two 30-iteration loops computing the dgemm        | )3 |

| 0.0  | kernel using HIS and OmpSs                                              | 94 |

|      | Retifer using this and Onipos                                           | クサ |

# **List of Tables**

| 3.1 | REPHRASE attributes                                                       | 24 |

|-----|---------------------------------------------------------------------------|----|

| 3.2 | Results for the Rodinia benchmark suite. P, F and M stand for the         |    |

|     | number of Pipeline, Farm and Map patterns detected, respectively          | 30 |

| 3.3 | Results for the NAS benchmark suite. P, F and M stand for the number      |    |

|     | of Pipeline, Farm and Map patterns detected, respectively                 | 30 |

| 4.1 | Parallel patterns compositions in GRPPI                                   | 48 |

|     | Percentage of increase of lines of code w.r.t. the sequential version for |    |

|     | the video application.                                                    | 51 |

| 5.1 | PIBA working example.                                                     | 68 |

# Chapter 1

# Introduction

In recent years, the traditional approaches for improving CPU performance, such as increasing clock speed, has come to a dead-end because of physical constraints. To tackle this issue, the appearing of parallel architectures, such as multi-/many-core processors, allows increasing the performance by providing greater processing capabilities. Furthermore, with the emerging trend of heterogeneous platforms, comprising nodes with multi-/many-core CPUs, coprocessors, and accelerators, developers have started to leverage the advantages provided by the different computing units as these platforms allow to improve performance and energy efficiency better than other alternatives.

However, although most of the current computing hardware has been envisioned for parallel computing, much of the prevailing production software is still sequential [83]. In other words, a large portion of the computing resources provided by modern architectures is basically underused. In order to exploit these resources, it is necessary to refactor sequential software into parallel. However, platforms comprising diverse devices are notoriously more difficult to program effectively, since they demand distinct frameworks and programming interfaces [47].

This chapter introduces the background of this thesis. Section 1.1 explains the motivation for this work in the aforementioned context. Section 1.2 defines the goals and expected contributions of this work. Finally, this section outlines the structure of the rest of the document.

#### 1.1 Motivation

As mentioned, the computational elements used in heterogeneous platforms provides performance improvements thanks to their parallel capabilities. However, programming efficiently for these architectures demands big efforts in order to transform sequential applications into parallel and to optimize such applications. Compared to sequential programming, designing and implementing parallel applications for operating on modern hardware poses a number of new challenges to developers [5]. Communication overheads, load imbalance, poor data locality, improper data layouts, contention in parallel I/O, deadlocks, starvation or the appearance of data races in threaded environments are just examples of those challenges. Besides, maintaining and migrating such applications to other parallel platforms demands considerable efforts. Thus, it becomes clear that programmers require additional expertise and endeavor to implement parallel applications, apart from the knowledge needed in the application domain.

To tackle this issue, several solutions in the area, such as parallel programming frameworks, have been developed to efficiently exploit parallel computing architectures [77]. Indeed, multiple parallel programming frameworks from the state-of-the-art benefit from shared memory multi-core architectures, such as OpenMP,

Cilk or Intel TBB; distributed platforms, such as MPI or Hadoop; and some others especially tailored for accelerators, as e.g., OpenCL and CUDA. Basically, these frameworks provide a set of parallel algorithmic skeletons (e.g. parallel\_for or parallel\_reduce) representing recurrent algorithmic structures that allow running pieces of source code in parallel. Nevertheless, only a small portion of production software is using these frameworks. Although all these skeletons aim to simplify the development of parallel applications, there is not a unified standard [32]. Therefore, users require understanding different frameworks, not only to decide which fits best for their purposes but also to properly use them. Not to mention the migration efforts of applications among frameworks, which becomes as well an arduous task. In this sense, a good practice to implement more robust, readable and portable solutions is the use of design patterns that provide a way to encapsulate (using a building blocks approach) algorithmic aspects with such a high-level of abstraction. Examples of applications coming from multiple domains (e.g., financial, medical and mathematical) and improving their performance through parallel programming design patterns, can be widely found in the literature [17, 45, 59].

However, in order to parallelize these applications, it is necessary to analyze the sequential code in order to detect the regions of code that can be parallelized using parallel patterns. A solution to parallelize these codes is to manually translate into parallel code, however this task results, in most cases, cumbersome and very complex for large applications. Another solution is to use refactoring tools, applications that advice developers or even semi-automatically transform sequential code into parallel [12]. Although source codes transformed using these techniques do not often get the best performance, they aid in reducing necessary refactoring time [57].

Unfortunately, refactoring tools found are still premature, not yet being fully adopted by development centers. In fact, many of them are human-supervised, being the developer the only responsible for providing specific sections of the code to be refactored. Although these tools relieve the burden of the source-to-source transformation, this process still remains semi-automatic. Key components for turning this process from semi- to full-automatic are parallel pattern detection tools. This situation motivates the purpose of this thesis: design a toolchain to automatically transform sequential codes into parallel and ease the development and optimization of parallel applications.

# 1.2 Objetives

In light of the growing necessity of transforming sequential applications into parallel, as well as reducing the complexity of modern parallel programming models, we define the following goal for this Thesis:

**Goal:** The main goal of this Thesis is to provide a tool-chain capable of detecting parallel patterns in sequential code and transform them into optimized parallel code by leveraging a unified interface, designed to act as a layer between developers and different parallel programming frameworks.

This goal can be divided in the following specific goals:

1. To develop automated techniques to detect parallel patterns. This tool will be able to detect parallel patterns in sequential code, diminishing the efforts required to analyze the code. The result will be an annotated source code determining the potential candidates to be refactored.

- 2. To define a unified interface for parallel patterns. This interface will act as a layer between the users and different parallel programming frameworks and, therefore, easing the development of parallel applications. Furthermore, parallel patterns supported by this interface will also be composable among them in order to build more complex constructions.

- 3. **To develop automated transformation techniques.** This transformation will take the annotated code in order to generate parallel code using the generic and unified interface proposed in this thesis. With this tool, the refactoring process will become automatic and, thus, reducing the efforts to transform the code.

- 4. To define a mechanism to optimize parallel constructions. During the refactoring process from sequential to parallel source code, some constructions could be further improved by rearranging compositions or by modifying execution parameters such as the concurrency degree. Therefore, this goal is to introduce a way to semi-automatically evaluate and generate better configurations and compositions of parallel patterns.

- 5. To develop a mechanism to select the most suitable implementations. This mechanism will allow selecting among different routine implementations depending on the problem size in order to provide, with a single interface, the most suitable version on each case.

#### 1.3 Document structure

The rest of this document is structured as follows: Chapter 2 reviews the state-of-the-art about existing technologies and techniques researched in the same line as the work proposed in this thesis. Chapter 3 explains in detail the parallel pattern analyzer tool that is able to automatically detect and annotate parallel patterns in sequential codes. Chapter 4 defines the generic and reusable parallel pattern interface. Chapter 5 describes the automatic refactoring and optimization of parallel constructions for some stream-oriented parallel patterns. Chapter 6 describes the proposed mechanisms to select among different routine implementations. Finally, Chapter 7 enumerates some concluding remarks and future works.

# **Chapter 2**

# State of the art

This chapter provides the background and previous works that act as the base for the rest of the work presented in this thesis.

Firstly, Section 2.1 introduces the definition of parallel computing and presents some of the current architectures and processors. In order to efficiently exploit the resources provided by these platforms, Section 2.2 revisits different parallel frameworks from the state of the art that provide a way to express parallelism while minimizing the efforts of the parallelization task. Afterward, Section 2.3 describes the parallel patterns that will be supported by the proposed generic parallel pattern interface, one of the key points of this thesis. These patterns encapsulate algorithmic aspects allowing to ease the task of designing and developing parallel applications.

As mentioned in the previous chapter, transforming sequential code into parallel is a time-consuming and error-prone task, which demands an additional expertise and endeavor from developers. Therefore, another key point of this Thesis is the automated parallel region detection and code transformation. In Section 2.4, we discuss the state-of-the-art regarding code transformation techniques and tools.

Lastly, since different implementations of the same routine behave differently on concrete architectures, it is necessary to select which version provides the best performance in each case. In this sense, Section 2.5 reviews the research about multiple implementations selection techniques.

#### 2.1 Parallel architectures

With the end of the traditional improvements in computing architectures, such as the increase of clock frequency, has led to the widespread adoption of parallel architectures that provides a way to increase the number of operations that can be performed at the same time. In this sense, following Flynn's taxonomy, modern architectures leverages two major strategies to provide these parallel capabilities: Single Instruction Multiple Data (SIMD) and Multiple Instruction Multiple Data (MIMD)[19].

#### • Single Instruction Multiple Data

This strategy is based on applying the same instruction or operation at the same time on a given data set. In this case, the parallel units of a given architecture share the same instructions but apply them to different data elements [71]. Usually, this kind of architectures employs a control unit that emits the same instruction stream to multiple execution units that applies the same instruction to different data in a synchronous manner. This way a same copy of the code can be executed simultaneously, and thus, reducing the necessary instruction bandwidth and space. Examples of technologies that take advantage of this kind of architectures are the vector instructions implemented on modern processors and the Graphic Processing Units (GPUs).

Focusing on vector instructions we can find the Advanced Vector Extensions (AVX), the successor of the Streaming SIMD Extensions (SSE) [38], implemented on modern Intel and AMD processors. In general AVX are extensions to the instruction sets of x86 architectures that allow applying the same operation over a multiple data elements. These instructions leverage registers of 256-bit that may contain eight 32-bit single-precision or four 64-bit double precision floating point numbers. Additionally, these registers and instruction have been extended to 512-bit (AVX-512) in recent Intel architectures such as Intel Xeon Phi Knight Landing and some Intel Skylake CPUs [36].

• Multiple Instruction Multiple Data On the contrary to the previous strategy, in this case, the parallel units do not share instructions or data. This way, each parallel unit may perform different operations over different data at the same time. In other words, processors in these architectures work in an autonomous way. However, the software exploiting these architectures requires to leverage techniques to synchronize the work performed by each process, e.g. by accessing some shared data on shared memory architectures or by passing messages via interconnection networks. Basically, we can distinguish two main architecture designs that follow this strategy: shared memory and distributed memory.

On the one hand, shared memory architectures share the main memory, and in some architectures even cache memory, among the different cores or CPUs in the same platform. This way, processes working in these architectures are able to modify information in a memory that can be seen by other processes in the platform in order to communicate them. Depending on the distances to the memory to the different processing units, we can distinguish two kind of memory sharing: Uniform Memory Access (UMA) in which the distance to the memory from each unit is the same, i.e. the latency of accessing the memory is the same; and Non-uniform Memory Access (NUMA) where the memory access time depends on the memory location relative to a given processor. Some examples of these architectures are the multi-/many-core processors as an example of UMA architectures and multi-socket or NUMA-multiprocessor architectures as an example of NUMA architectures.

On the other hand, distributed systems are similar to a multi-processor architecture in that they do not share memory among the different processors (nodes) in the system. In contrast to shared-memory architectures, data cannot be directly shared among processors but transmitted through an interconnection network. This interconnection network among the different nodes in the distributed system is usually implemented by using high-speed standard communication protocols, such as Gigabit Ethernet or infiniband. However, data communication has non-negligible overheads due to network communication latencies. Thus the topology of the network becomes really important to diminish these latencies. On the other hand, these architectures can be easily grown by just adding new nodes to the system. Additionally, these systems also use shared-memory in each of the nodes comprising the distributed system. A representative example of these architectures are clusters, where each node interconnected to a specific network can be equipped with one or more shared-memory processors.

Up to this point, we have discussed the most common paradigms or strategies (SIMD and MIMD), however current platforms are equipped with multiple devices

that take advantage of both paradigms. These platforms are usually named heterogeneous platforms that are comprised of one or multiple CPUs, each of them potentially with a vector unit, GPUs, accelerators and/or co-processors. This way the parallel resources have been widely increased and multiple operations can be performed at the same time by a given application. However, most of the production software is still sequential, thus even if the resources are available to be exploited by parallel applications they are still under-used. The main reason for this situation is that a big portion of that software consists of legacy applications, and transforming them into parallel is an expensive task which requires additional expertise in parallel programming by the developers.

#### 2.2 Parallel Programming Models

As commented, sequential legacy applications do not take advantage of current parallel architectures and, therefore, under-exploit its parallel resources. However, transforming sequential code into parallel present major challenges to developers, since it requires additional expertise in parallel programming and it does not always provide performance improvements. This is mainly due to the inherent complexities of parallel programming such as synchronizations, data locality or load balance. To tackle these issues, multiple parallel programming models have been developed to alleviate the burden of parallelization.

In this section, we revisit some parallel programming models from the state-of-the-art developed to ease the development of parallel programming. Concretely, Section 2.2.1 classifies the different ways in which the parallelism is expressed in the programming models. Finally, Sections 2.2.2 and 2.2.3 provide a survey of different well-known programming models from the state of the art classified as low-level and high-level frameworks.

#### 2.2.1 Types of parallelism

This section provides a classification of the parallel programming models from the state-of-the-art depending on the parallelism that can be expressed. Specifically, we distinguish three different types of parallelism: *Task-parallelism*, *Data-parallelism* and *Stream-parallelism*.

**Task-parallelism** This type of parallelism consists on executing distinct and independent computations on different execution entities (e.g. threads). This computations, namely tasks, can be communicated by sending the data among them constituting a task dependency graph. Usually, programming models that provide this kind of parallelism implement a runtime to execute the task when its dependencies have been satisfied.

**Data-parallelism** is based on dividing a data set among the different parallel entities and processing them independently. This kind of parallelism requires that the computations of each data element should be stateless, i.e, the processing of a data element cannot have any dependencies of any other element and the output value should not depend on state values.

**Stream-parallelism** This type of parallelism is based on computing in parallel the processing of elements arriving into an input stream. This parallel processing is

based on splitting the whole computation into different tasks that can be parallel tasks if the task can be applied in parallel to multiple elements, or sequential task if it is stateful and only one element at a time can be processed. Note that, in this case, as a major difference with *Data-parallelism*, the whole data set is not usually available at the beginning and the data elements might become available over time, e.g. readings from a sensor or requests received from a network connection.

#### 2.2.2 Low-level parallel frameworks

As introduced, we classify the parallel programming into two categories: *low-level* and *high-level* parallel frameworks. *Low-level* parallel frameworks cover those that do not provide abstractions over the parallel platform. In this sense, those frameworks demand deeper knowledge of the underlying platform and usually require to manually introduce synchronization primitives, explicitly determine mutual exclusion regions or manage the data sharing.

Next, we introduce some well-known *low-level* parallel programming models from the state-of-the-art.

**ISO C++ Threads** The C++ thread class, incorporated in the C++11 standard [40], represents an individual thread that executes a sequence of instructions concurrently with any other thread in the application on multithreaded environments. This class encapsulates the creation of a thread hiding away the actual call that depends on the specific operating system, e.g. pthread\_create() on Unix like systems. However, to communicate and/or synchronize threads using this feature requires to explicitly incorporate the concurrency mechanisms, e.g. mutexes or atomic variables. In this sense, programming parallel applications become complex due to the potential data dependencies, data races or deadlocks that should be managed by the developer.

Compute Unified Device Architecture CUDA is a set of tools and a compiler, developed by nVidia, that allows developers to express parallel applications targeted to Graphics Processing Units (GPUs) [63]. This framework uses an extension of the C++ language to leverage the GPU for coprocessing algorithms in parallel with the CPUs. Thanks to this framework is possible to take advantage of the SIMD capabilities provided by these architectures. In this sense, GPGPU programming is suitable for data-parallelism.

However, in order to properly leverage these architectures, is it necessary to explicitly determine the data communication between the "Host" (CPU) and the "Device" (GPU). This communication leads to overheads related to the data transfers since both CPU and GPU do not share the same memory address space. Therefore, dealing with these devices requires an additional effort to determine if the communication overheads are paid off by the performance improvement provided by them.

Open Computing Language Open Computing Language (OpenCL) is a parallel framework that allows implementing application targeted to heterogeneous platforms comprised of multi-/many-core processors, GPUs, digital signal processors (DSPs) and/or field programmable gate arrays (FPGAs) [82]. This framework, similar to CUDA, follows a host-device approach. In other words, thanks to this framework the host (CPU) is able to launch compute functions, called "kernels", on the different computing devices available in the platform. The main advantage of this

programming framework is that the same source code can run on multiple architectures without modifying it. However, it is necessary to explicitly manage the data transfers between host and device and it requires to tune the application in order to better exploit the available resources. Furthermore, the original sequential code requires deep refactoring in order to leverage OpenCL for improving the performance of a given application.

Message Passing Interface Message Passing Interface (MPI) is a standard that defines the syntax and semantics of the function provided by a given library implementing it [26]. This interface defines a way to effectively program concurrent applications on multiprocessing environments such as "clusters". Several implementations of this standard can be found on the state-of-the-art such as MPICH [33] or OpenMPI [27]. These frameworks provide synchronization and communication between processes that may run in different processors, e.g. cores in the same CPU or different CPUs on different machines. This way, using these mechanisms, multiple processes can run concurrently on the same application. However, the communication and synchronization should be explicitly incorporated in the application by means of sending or receiving messages to/from other processes. Therefore, it becomes clear that efficient use of these mechanisms requires a profound knowledge of both the framework and the target application in order to determine when and what should be passed between processes.

#### 2.2.3 High-level parallel frameworks

In the previous section, we have discussed *low-level* parallel frameworks that allow developers to implement parallel applications. This kind of frameworks provide a way to express parallelism in a low-level way, and consequently, allow to fully optimize the code to the target platform and better exploit the available resources. However, these benefits come with a wide number of challenges, it is necessary to know the target platform, properly use synchronization and communication primitives, be concerned about data sharing, etc. For these reasons, the resulting code is usually tied to the target platform which makes it difficult to migrate the application between different architectures [5]. Furthermore, when dealing with heterogeneous platforms comprised by multiple and diverse devices, it becomes even more complex to develop portable and maintainable code.

To tackle these issues, high-level approaches provide abstractions that allow implementing parallel applications hiding away the aforementioned complexities. Therefore, the resulting applications have improved portability and maintainability compared to those implemented using *low-level* frameworks. However, *high-level* frameworks usually do not provide the best possible performance due to the inherent abstraction overheads, but performs reasonably well in a wide range of parallel platforms [32].

In the following, we review different *high-level* frameworks from the state of the art.

**Open Multi Processing** Open Multi Processing (OpenMP) is an application programming interface targeted to shared memory platforms [67]. This programming framework is based on "pragma" annotations to determine code regions that can be processed in parallel. Basically, OpenMP abstracts the aspects related to thread and data management thanks to the different clauses that can be introduced along with the "pragmas". In this sense, OpenMP provides some higher-level abstractions

easing the parallelization task, however, it still requires to identify data dependencies, the scope of the variables in a parallel region and restrict the access of critical sections.

Intel Cilk Intel Cilk is an extension of C and C++ languages that allows taking advantage of multi-core architectures and vector instructions [8]. Similarly to the OpenMP framework, this extension provides support for task and data parallelism that is enabled via "pragma" annotations (e.g. simd) and specific keywords (e.g. \_Cilk\_for and \_Cilk\_spawn). Thanks to these keywords and "pragmas", the inherent complexities of parallel programming are alleviated. Additionally, this C++ language extension provides a collection of objects that allow protecting shared variables while maintaining the sequential semantics of the application (e.g. reducers). However, this programming model lacks high-level abstractions and it still requires to explicitly identify synchronization points.

**Intel Threading Building Blocks** Intel Threading Building Blocks (TBB) is a C++ template library targeted to multi-core processors [75]. This task-parallel library provides a set of algorithmic skeletons (e.g parallel\_for and pipeline) that hides away the complexities of thread management and synchronizations in such parallel constructions. Additionally, TBB incorporates a runtime scheduler that permits to execute the different task respecting the dependencies and to balance the parallel workload by leveraging a work-stealing approach. This way, this framework eases the development of parallel applications while decouples the underlying architecture from the source code.

**Fastflow** FastFlow is a structured data and stream parallel programming framework targeted to multi-core and GPU architectures [3]. This framework provides a set of algorithmic skeletons that models different parallel patterns such as Pipeline, Farm or Map. Basically, these constructs, implemented as C++ classes, allows encapsulating algorithmic features while hiding away complex thread communication and synchronization mechanisms. Additionally, the patterns supported by the framework can be composed among them in order to build more complex algorithmic constructs. In general, this framework reduces the parallel design and development efforts while improves the performance thanks to its high-level abstractions.

**SkePU** SkePU is a programming framework targeted to multicore and GPU architectures based on C++ templates [21]. This framework provides a collection of predefined generic components that implement specific computation patterns and data dependencies known as "skeletons". These skeletons receive the sequential user code encapsulating low-level and platform-specific details such as synchronizations, data management, and several optimizations. Additionally, this framework also supports multiple backends for sequential, OpenMP, OpenCL and CUDA.

Parallel Standard Template Library The parallel STL is a novel feature of C++17 [42] that provides parallel implementations of the algorithms present in the C++ standard library. These parallel algorithms support multiple execution policies that are used as an extra parameter with respect to the original STL algorithms to determine how the algorithm is computed, i.e. in sequential, parallel or vectorized. This extension is currently supported by the Intel Compiler and Microsoft Visual Studio Compiler [13].

2.3. Parallel Patterns 11

**High Performance ParallelX** High Performance ParallelX (HPX) is a general purpose C++ runtime for parallel and distributed application [44]. This library provides a set of parallel algorithms that extend the C++ standard library algorithms to be computed in parallel (Parallel STL) along with other utilities such as new container types or hardware counters support. The interface for the high-level algorithms is similar to that designed for this thesis and provides support for multiple execution policies. However, this interface lacks high-level patterns targeted to stream processing applications such as the farm or pipeline patterns.

**Muesli** The Münster Skeleton Library (Muesli) is a C++ programming framework targeted to heterogeneous and distributed platforms [22]. In this sense, this framework is able to generate different binaries aimed at multiple heterogeneous clusters and hides away the complexities of using specific frameworks, e.g. OpenMP, MPI or CUDA. This library provides support for multiple data parallel skeletons and for the farm pattern. However, it lacks stream processing skeletons.

**CUDA Thrust** CUDA thrust is a C++ template library based on the standard template library (STL) [66]. Basically, this framework allows implementing algorithms targeted to nVidia GPUs by using the collection of supported data parallel algorithms. Thus, using this interface similar to the STL, eases the development of applications targeted to GPUs without requiring additional expertise and knowledge about CUDA programming. However, this framework still requires to explicitly determine the host-device data transfers and to annotate the kernels with macros.

**SYCL** SYCL is a high-level programming framework that introduces an abstraction layer between the users and the OpenCL framework using an interface similar to the STL [46]. This library provides an implementation of the parallel STL by defining a new execution policy to support OpenCL. This way, the code developed using this framework becomes portable and cross-platform thanks to the OpenCL environment.

#### 2.3 Parallel Patterns

Patterns can be loosely defined as commonly recurring strategies for dealing with particular problems. This methodology has been widely used in multiple areas, such as architecture, object-oriented programming, and software architecture [53]. In this Thesis, we focus on patterns for parallel software design, as it has been recognized to be one of the best codifying practices [29]. This is mainly because patterns provide a mechanism to encapsulate algorithmic features, making them more robust, portable and reusable, while if tuned, they can achieve better parallel scalability and data locality. In general, parallel patterns can be categorized in three groups: data parallel patterns, e.g., Map, Reduce and MapReduce; task parallel patterns, e.g. Divide&Conquer; and stream parallel patterns, e.g., Pipeline, Farm and Filter [56]. Additionally, when dealing with stream processing, different kind of constructs, denoted as stream operators, can be found in the state-of-the-art in order to modify the stream flow, e.g. Window, Split-Join [6]. However, in some situations, these constructs do not match or need to be composed in a very complex way. Focusing on these situations, the advanced patterns model some domain-specific algorithms that cannot be

represented using basic patterns or simple compositions [73]. Following this classification, in the next sections, we describe formally the parallel patterns and stream operators leveraged in this Thesis.

#### 2.3.1 Data parallel patterns

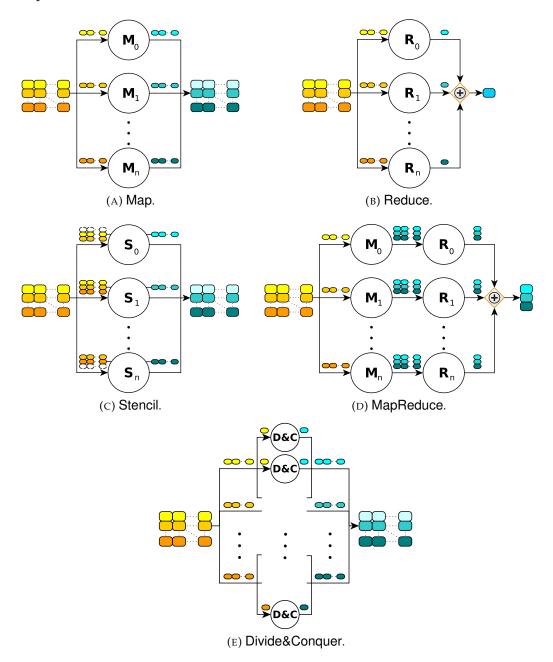

In this section, we describe formally the data parallel patterns Map, Reduce, Stencil, and MapReduce.

**Map** This data parallel pattern computes the function  $f:\alpha\to\beta$  over the elements of the input data collection, where the input and output elements are  $\alpha$  and  $\beta$  types, respectively (see Figure 2.1a). The output result is the collection of elements  $y_1,y_2,\ldots,y_N$ , where  $y_i=f(x_i)$  for each  $i=1,2,\ldots,N$  and  $x_i$  is the i-th element of the input collection. The only requirement of the Map pattern is that the function f should be pure, i.e. the function has no side effects.

**Reduce** This data parallel pattern aggregates the elements of the input data collection of type  $\alpha$  using the binary function  $\oplus: \alpha \times \alpha \to \alpha$ , that is usually associative and commutative. Finally, the result of the pattern is summarized in a single element y of type  $\alpha$  that is obtained performing the operation  $y = x_1 \oplus x_2 \oplus \ldots x_N$ , where  $x_i$  is the i-th data item of the input data collection (see Figure 2.1b). The main constraint of this pattern is that the binary function should be pure.

**Stencil** This pattern is a generalization of the Map pattern in which an elemental function can access, not only to a single element in an input collection but also to a set of neighbors (see Figure 2.1c). The function  $f: \alpha* \to \alpha$  used by the Stencil pattern receives the input item and a set of neighbors ( $\alpha*$ ) and produces an output element of the same type. The main requirement of this pattern is that the function f should be pure.

**MapReduce** This pattern computes, in a first stage a Map-like pattern, a key-value function over all the elements of an input collection, and delivers, in a second stage a Reduce-like pattern, a set of unique key value pairs where the value associated to the key is the "sum" of the values output for the same key (see Figure 2.1d). To do so, the MapReduce pattern computes in the Map function  $f: \alpha \to \{Key, \alpha\}$  the elements in the input collection; afterwards it uses the Reduce binary function  $\oplus: \beta \times \beta \to \beta$  to sum up the partial results with the same key. The result of this pattern is a collection of data elements of type  $\beta$ , one per key. The requirements of the MapReduce pattern is that both Map and Reduce-related functions should be pure.

#### 2.3.2 Task parallel patterns

In this section, we describe formally the task parallel pattern Divide&Conquer.

**Divide&Conquer** This pattern computes a problem by means of breaking it down into two or more subproblems of the same kind until the base case is reached and solved directly. Afterward, the solutions of the subproblems are merged to provide a solution to the original problem (see Figure 2.1e). In other words, this pattern applies the function  $f: \alpha* \to \beta*$  on a collection of elements of type  $\alpha$  and produces a collection of elements of type  $\beta$ . A divide function  $\mathcal D$  is used first to split the collection into distinct partitions up to the size of the base problem, which can be solved

2.3. Parallel Patterns 13

directly applying f. Finally, the partial results of the base problems are combined according to a merge function  $\mathcal M$  in order to build the final output collection. The requirements of the Divide&Conquer pattern are that the functions f,  $\mathcal S$  and  $\mathcal M$  should be pure.

FIGURE 2.1: Data parallel patterns.

#### 2.3.3 Stream parallel patterns

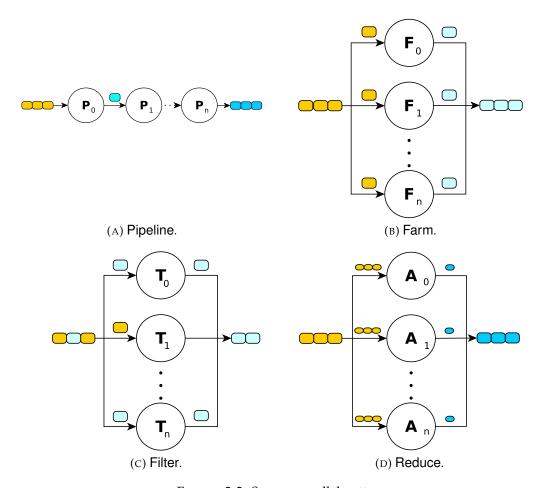

In this section, we describe formally the stream parallel patterns Pipeline, Farm, Filter, and Reduce.

**Pipeline** This pattern processes the items appearing on the input stream in several parallel stages (see Figure 2.2(a)). Each stage of this pattern processes data produced by the previous stage in the pipe and delivers results to the next one. Provided that

the *i*-th stage in a *n*-staged Pipeline computes the function  $f_i: \alpha \to \beta$ , the Pipeline delivers the item  $x_i$  to the output stream applying the function  $f_n(f_{n-1}(\dots f_1(x_i)\dots))$ . The main requirement of this pattern is that the functions related to the stages should be pure, i.e., they can be computed in parallel without side effects.

**Farm** This pattern computes in parallel the function  $f: \alpha \to \beta$  over all the items appearing in the input stream (see Figure 2.2(b)). Thus, for each item  $x_i$  on the input stream the Farm pattern delivers an item to the output stream as  $f(x_i)$ . In this pattern, the computations performed by f for the items in the input stream should be completely independent of each other, otherwise, they cannot be processed in parallel.

**Filter** This pattern computes in parallel a filter over the items appearing on the input stream, passing only to the output stream those items satisfying the boolean "filter" function (or predicate)  $\mathcal{P}: \alpha \to \{true, false\}$  (see Figure 2.2(c)). Basically, the pattern receives a sequence of input items ...,  $x_{i+1}, x_i, x_{i-1}, \ldots$  and produces a sequence of output items of the same type but with different cardinality. The evaluation of the filtering function on an input item should be independent to any other, i.e., the predicate should be a pure function.

**Reduce** This pattern collapses items appearing on the input stream and delivers these results to the output stream (see Figure 2.2(d)). The function used to collapse item values  $\oplus$  should be a pure binary function of type  $\oplus$  :  $\alpha \times \alpha \to \alpha$ , being usually associative and commutative. Basically, the pattern computes the function  $\oplus$  over a finite sequence of input items ...,  $x_{i+1}, x_i, x_{i-1}, \ldots$  to produce a collapsed item on the output stream. The number of elements to be accumulated depends on the window size set as a parameter.

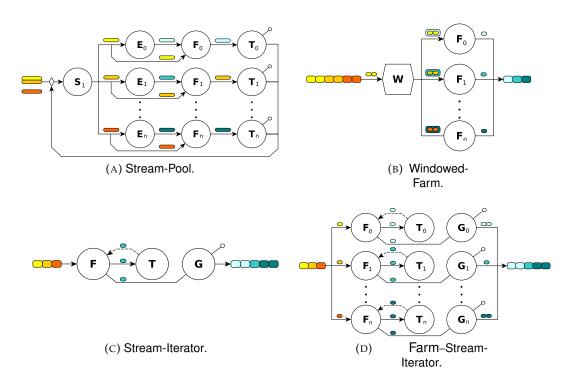

#### 2.3.4 Stream operators

The stream operators are designed to work cooperatively with other patterns in order to provide a way of expressing more complex constructions. Specifically, they are intended to modify the stream flow in different ways. In this section, we describe the Split-Join and the Window stream operators along with their different configurations.

**Split-Join** This stream operator distributes, in a first Split phase, a data stream into different substreams which can be processed in parallel applying different transformations. Afterwards, a Join phase combines the substreams into a single one (see Fig. 2.3(a)). This operator is characterized by the different distribution and combining policies that can be applied in both Split and Join phases. The supported policies are the following two:

**Duplication** This policy duplicates the data items appearing on the input stream to each of the different substreams. In other words, when an item of type  $\alpha$  arrives at the input stream, this is copied into every substream. By definition, this policy can only be applied in the Split phase of the Split-Join operator.

**Round-robin** This policy can be applied in both Split and Join phases. If applied on the Split phase, the data items of type  $\alpha$  appearing on the input stream are delivered following a round-robin policy onto the substreams. On the other

2.3. Parallel Patterns 15

FIGURE 2.2: Stream parallel patterns.

hand, if used on the Join phase, the items delivered at the end of the substreams are combined together into the main data stream employing the same policy. In this distribution policy the slice size, i.e. the number of consecutive items that should be taken from the source stream, can be freely configured.

**Window** This stream operator takes the data items from the input stream and delivers collections of items (windows) to the output stream (see Fig. 2.3(b)). Depending on how the windows are internally managed by this operator, different windowing policies can be set. The following policies can be portrayed based on what and how many items are part of the same window.

**Count-based** This policy is characterized by managing windows of fixed size, i.e., capable of holding up a maximum number of items. Note that the user should specify the window size. The rationale of this policy is the following: when a new item of type  $\alpha$  arrives at the input stream, this is included in the window and the oldest is flushed. As soon as the window is complete, it is delivered to the output stream.

**Delta-based** This policy requires a  $\delta$  threshold value and a monotonic increasing  $(\Delta)$  attribute included in the input items. With these parameters, the *delta-based* policy is able to build a window of variable size. The items conforming a window are only those whose difference between the  $\Delta$  attribute of the latest item and the current one is less or equal than the given  $\delta$  threshold. Similar

to the *count-based* policy, when a window is built it is forwarded to the output stream.

**Time-based** This policy keeps an internal wall-clock and labels each input item with a timestamp indicating their arrival time. Additionally, it requires the users to specify a time threshold ( $\tau$ ). This information allows the policy to build windows including the items that arrived in the last time, as specified by  $\tau$ . For instance, a threshold of 60 s would conform windows including items that arrived at the last minute.

**Punctuation-based** This policy needs a *punctuation* value/symbol that indicates the end of a window. In other words, it delivers a new window each time a new item matching the *punctuation* value is received. For instance, considering a stream of words belonging to a text and using the "." character as for the punctuation symbol, this policy would conform windows containing the sentences in the text.

Note that the count-, delta- and time-based windowing policies support an overlap factor, i.e., the number of items in the window  $w_i$  that are also part of the window  $w_{i+1}$ .

FIGURE 2.3: Stream operators.

#### 2.3.5 Advanced stream parallel patterns

In this section, we describe some advanced stream parallel patterns, designed for those scenarios in which the basic patterns do not match any of these constructs or have to be composed in a very complex way.

**Stream-Pool** This pattern models the evolution of a population of individuals matching many evolutionary computing algorithms in the state-of-the-art [4]. Specifically, the Stream-Pool pattern is comprised of four different functions that are applied iteratively to the individuals of type  $\alpha$  belonging to a population P managed as a stream (see Figure 2.4(a)). First, the *selection* function S:  $\alpha^* \to \alpha^*$  selects a subset of individuals belonging to P. Next, the selected individuals are processed by means of the *evolution* function E:  $\alpha^* \to \alpha^*$ , which may produce any number of new or modified individuals. The resulting set of individuals, computed by E, are filtered through a *filter* function F:  $\alpha^* \to \alpha^*$ , and eventually inserted into the input stream (population). Finally, the *termination* function T:  $\alpha^* \to \{true, false\}$  determines in each iteration whether the evolution process should be finished or continued. To guarantee the correctness of the parallel version of this pattern, the functions E, F and T should be pure, i.e., they can be computed in parallel with no side effects.

**Windowed-Farm** This pattern delivers "windows" of processed items to the output stream. Basically, this pattern applies the function F over consecutive contiguous collections of x input items of type  $\alpha$  and delivers the resulting windows of y items of type  $\beta$  to the output stream (see Figure 2.4(b)). Note that this pattern simplifies the composition of the Window and Farm patterns. Also, the windows produced by this pattern benefit from the same windowing policies provided by the Window stream operator. The parallelization of this pattern requires a pure function F:  $\alpha^* \to \beta^*$  for processing windows.

**Stream-Iterator** This pattern is intended to recurrently compute the pure function  $F: \alpha \to \alpha$  on a single stream input item until a specific condition, determined by the boolean function  $T: \alpha \to \{true, false\}$ , is met. Additionally, in each iteration the result of the function F is delivered to the output stream, depending on a boolean output guard function  $G: \alpha \to \{true, false\}$  (see Figure 2.4(c)). Note that this pattern, due to its nature, does not provide any parallelism degree by itself and can be classified as a pattern modifier. Therefore, the parallel version of this construct is only achieved when it is used in cooperation with some other core stream pattern, e.g., using Farm or Pipeline as for the function F. An example of Stream-Iterator composed with a Farm pattern is shown in Figure 2.4(d).

FIGURE 2.4: Advanced parallel patterns.

# 2.4 Parallel region detection techniques

Although parallel patterns and high-level programming frameworks alleviate the burden of developing parallel applications, this task is still time-consuming and error-prone. In this sense, automatically detecting regions that can be parallelized and its corresponding transformation from sequential to parallel are key points to reduce the complexities of parallel programming [1]. In general, in order to achieve

this automatic parallelization, we classify the approaches from the state-of-the-art into two different groups: *i*) dynamic approaches based on profiling and code instrumentation; and *ii*) static approaches that rely on analyzing the code directly.

On the one hand, the dynamic approaches usually depend on executing the application that has been previously instrumented. These tools collect information about different characteristics of the application, e.g. memory accesses or write operations, and determines data dependencies. Next, with this information, they are able to determine if a region can be parallelized by analyzing data dependencies occurred during the execution. However, these approaches have some limitations: *i*) they have non-negligible overheads due to instrumentation and the required execution to perform the postmortem analysis; *ii*) since the analysis relies on the execution profile, if a data dependency is not revealed in a given run, it may lose it and give an erroneous analysis; and *iii*) the instrumentation techniques usually lose semantic information of the original code, and thus, making harder to link the profile with the source code.

On the other hand, static approaches rely on analyzing the code without executing it. In other words, they leverage the structures generated during the compilation to analyze data dependencies and determine if a code region can be parallelized. In this sense, these approaches, since they do not use profiling techniques, require less time to perform their analysis. Additionally, as they use the structures generated at compile time, they can also leverage semantic information present in the source code and it is easier to perform source-to-source transformations. However, these techniques are usually based on approximations, so they have to deal with false-positives/negatives. For instance, some data dependencies can be difficult to detect at compile time, e.g. aliasing or access to double-indexed matrices, and it can be determined as a dependency or not depending on which approximation is used.

In this section, we revisit some research works in the state-of-the-art that addresses the detection of potential parallel codes and refactoring processes.

#### 2.4.1 Dynamic approaches

Focusing on dynamic approaches for detecting potential parallel regions, multiple works can be found in the state-of-the-art. For example, the approach developed by Sean Rul et al. [76] leverages LLVM to instrument loops in the sequential code and performs an LLVM-IR profiling analysis to decide whether a loop is a pipeline or not. After that, it transforms the code to produce a parallel source code. However, this tool presents some shortcomings: it needs to execute the target application several times and profile it. Also, it is tied to the C programming language which allows some simplifications that cannot be made in C++. Similarly, Intel Advisor [37] performs profiling analysis in order to detect regions of code (loops) that can benefit from parallelization via threading or vectorization. Using the data collected during the profiling phase, it uses a Cache-Aware Roofline Model [51] in order to estimate the attainable performance of a given source code. Afterward, it provides a comparison for different parallel implementation alternatives.

Orthogonally, some works take advantage of functional languages. For instance, István Bozó et al. [9] develop a tool that analyzes and detects parallel patterns in applications written in Erlang in a semi-automated fashion. In a first stage, the tool performs an static analysis to detect potential parallel patterns and, afterward, it decides which pattern suits best for a given problem by using profiling techniques.

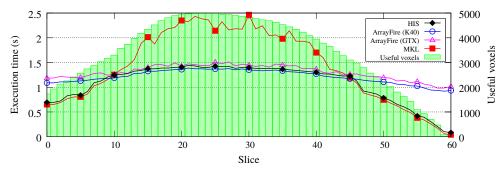

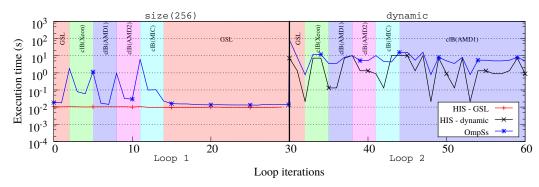

#### 2.4.2 Static approaches